広範囲の負電圧から正電圧を得る回路:Design Ideas パワー関連と電源(2/2 ページ)

出力電流が200mAで80%を超える変換効率

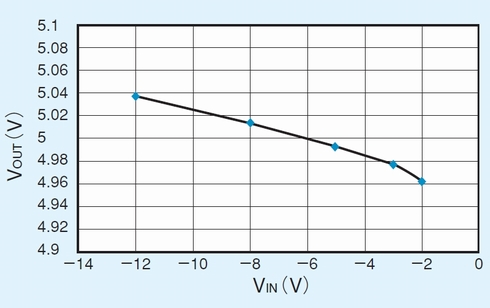

図2は、負電圧入力が変化したときの正電圧出力を示す。入出力間の最大電位差は、コンバーターICに内蔵されたスイッチング素子(パワーMOSFET)のドレイン‐ソース間耐圧(VDS)よりも大きくなってはならない。

今回使用したコンバーターICのVDSは18Vである。一方、図1における入出力間の最大電位差は17Vになる。入力電圧の最小値が−12V、出力電圧が5Vであるからだ。従ってVDSに対して1Vのマージンを確保できる。このマージンによって、ダイオードD1による電圧降下と、パワーMOSFETのドレイン電極における電圧スパイクを補償することが可能である。

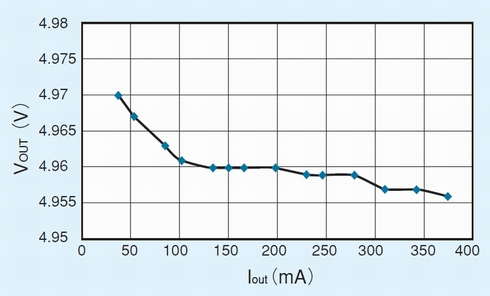

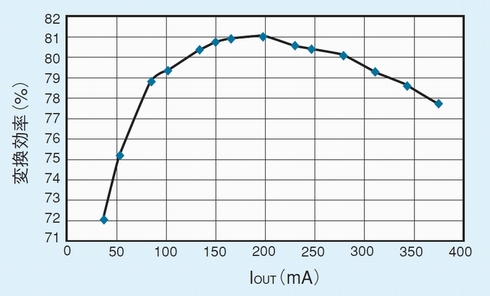

図3に、負荷が変化した場合に出力電圧がどの程度変化するかを示した。出力電流(IOUT)の最大値は、入力電圧と出力電圧の比やコンバーターICの電流制限の設定値に依存する。この回路の変換効率を図4に示す。出力電流が200mAのときに80%を超える変換効率を達成できる。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

関連記事

電池残量検出ICの電流スパイク耐性を高める

電池残量検出ICの電流スパイク耐性を高める

今回は、電流検出ICの電流スパイク耐性を、さまざまな側面から改善する回路を紹介する。 DC/DCコンバータの周辺部品削減と安定化

DC/DCコンバータの周辺部品削減と安定化

PWM方式絶縁型DC/DCコンバータの高性能フィードバック回路は多くの場合、誤差増幅器が使用される。今回は、部品点数を削減し、安定性を高めることができるフィードバック回路を紹介する。 スルーレート制御で電源のEMIを減らす

スルーレート制御で電源のEMIを減らす

オフラインのスイッチング電源が放射する電磁雑音(EMI)は電源回路全体に影響を与えるため、さまざまな問題が発生する。基板レイアウトは特に重要だ。今回は、電圧と電流のスルーレートを閉ループ回路で制御することで雑音を低減する回路を紹介する。 LDO型リニアレギュレータで実現する定電流源

LDO型リニアレギュレータで実現する定電流源

リニアレギュレータの電圧出力端子とグラウンド端子との間に固定抵抗を挿入すると、簡単に定電流源を構成できる。レギュレータの出力は定電圧であり、抵抗値が固定であれば、その両端を流れる電流は一定となる。今回は、負荷の高電位側にも低電位側にも定電流源を配置できる回路を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.