モデルベースデザイン手法を使ったProgrammable SoCの協調設計【実践編II】:HDLコード生成から統合検証まで(1/5 ページ)

「モデルベースデザイン手法を使ったProgrammable SoCの協調設計」とはどのようなものか、実践を交えて解説していく本連載。最終回の今回は、実装用モデルによる統合シミュレーションから、HDL/Cコード生成、そして統合検証まで行います。

昨今、さまざまな用途での利用が増えているFPGAとプロセッサを1チップ化した「Programmable SoC」。本連載ではProgrammable SoCの1つである「Zynq」(ザイリンクス製)のプロセッサとFPGAの両方を使ったアルゴリズム、つまりソフトウェア、ハードウェアで協調動作するアルゴリズムを、MATLAB/Simulinkを用いたモデルベースデザイン手法により実装する方法を解説しています。

前回は、「1. レファレンスモデル作成」から、「4. FPGA用サブシステム作成」までを説明しました。今回は、残りの実装作業について紹介し、実装を終えましょう。

本連載では、実装方法を分かりやすく解説するため「シンプルな構成の画像処理アルゴリズムを使った緑色のオブジェクト検出とトラッキングを行いつつ、赤い円形のマーカーを表示するアルゴリズムを実装する方法」を例に挙げて解説しています。なお、使用しているボードはAvnet(アヴネット)製の「ZedBoard」と、ザイリンクス製「ZC706」です。なおZC706は「ZC702」でも代用可能です。

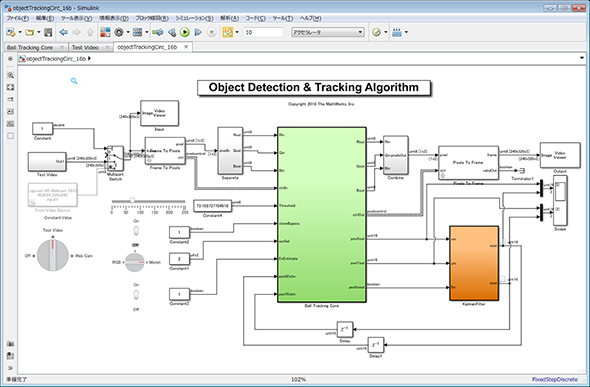

5.実装用モデルによる統合シミュレーション

プロセッサ用モデルとFPGA用モデルは、1つのモデル上で統合してシミュレーションを行います。連携して動作させた際のインタフェース仕様の整合性やレファレンスモデルとの等価性などを検証します。開発の早い段階で統合シミュレーションを行うことでさまざまな機能的な不具合を早期に発見し、大幅に手戻りを削減することが可能です。抽象度が低くなった分、シミュレーション速度は低下しますので、ここでの試行錯誤は最低限に抑えたいところです。図10に統合した実装用モデルを示します。

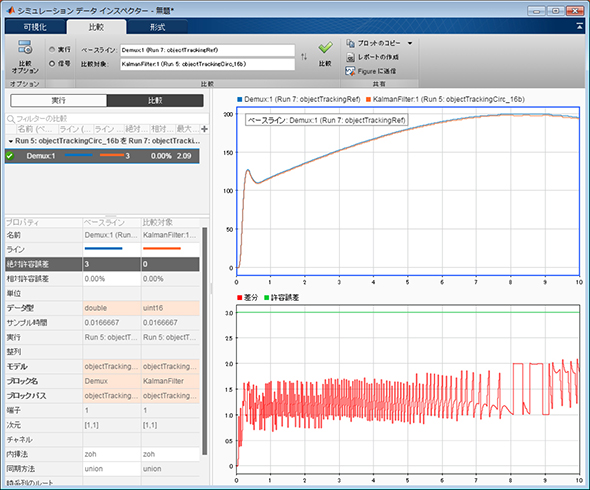

レファレンスモデルと実装用モデルの等価性を検証するには、それぞれのモデルの信号線でログを取り、シミュレーションデータインスペクター使って両方の結果波形を比較します。シミュレーションデータインスペクターは、複数モデルでロギングした信号を表示、比較し、設定した許容誤差をクリアしているかどうかを判断します。図11で示した例では、同一のテスト映像データを入力した際の、トラッキングしたオブジェクトの座標の推移を比較しています。レファレンスモデルと実装用モデルでは、演算精度や実装用モデルにするためのモディファイにより、いくらかの誤差が発生しますが、それが許容範囲に収まっているかどうかはこのようにして確認できます。

Copyright © ITmedia, Inc. All Rights Reserved.

図3(再掲):

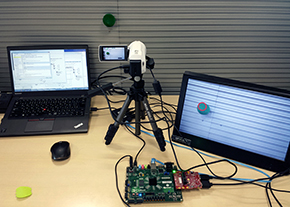

図3(再掲): 図1(再掲):Zynq搭載ボードによるオブジェクト検出とトラッキング

図1(再掲):Zynq搭載ボードによるオブジェクト検出とトラッキング