なんだこの設計は! メーカーの資質を疑う醜い回路設計:Wired, Weird(2/3 ページ)

論理不良の有無から確認

さてCMOSロジックIC 4000シリーズの調査に戻る。まず動作状態の論理不良の有無を調べるため、12Vの電源を入れてICの入力と出力を確認した。基板全体の消費電流は80mAだった。CMOSロジックICの基板にしては消費電流が少し多いようだ。実装されたICのピンアサインをデータシートで確認しながら全てのICの入出力端子の電圧を確認した。その結果、論理上は正常な値で、Low側は0.2V以下、High側は11.8V以上だった。問題がある論理のICは見つからなかった。

20個もの入力端子が……

CMOSロジックICで他に不具合があるとすると、入力端子がオープンのままでプルアップかプルダウン処理がされていない可能性がある。これを確認するため100kΩの抵抗を12Vでプルアップした治具を作った。この治具を端子に当て、電圧が12Vと表示されれば、その端子はオープンになっていると判別できる仕組みだ。この治具を当てた結果、28個の入力端子がオープンだった。8個の端子は元々がNC端子だったのでオープンで正常といえるが、残り20個もの入力端子がオープンになっているという結果は、かなりまずい設計だ。

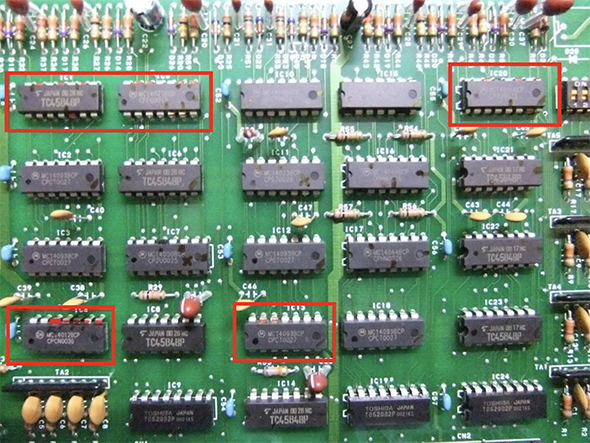

図3に入力がオープンになっていた端子に赤マークをつけ、該当するICを赤四角でマークした写真を示す。

入力端子がオープンになっていたICの数は、図3の通り5個だった。これは、CMOSロジックICの使い方を正しく教わらずに、回路設計を行った可能性が高い。CMOSロジックICの入力をオープンにするようなレベルの低い設計ミスは今では初心者でもしないだろう。まして12Vで入力をオープンにするとICがラッチアップし、焼損する危険性さえある。信じられない設計だ。

依頼主に回路変更を提案

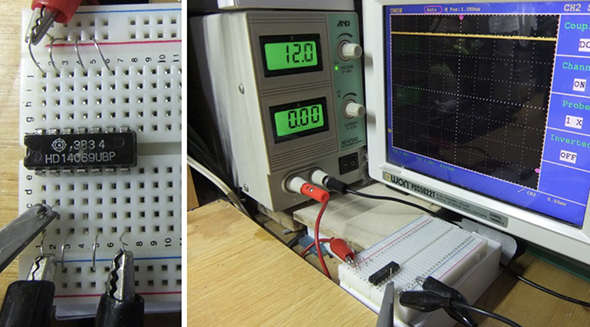

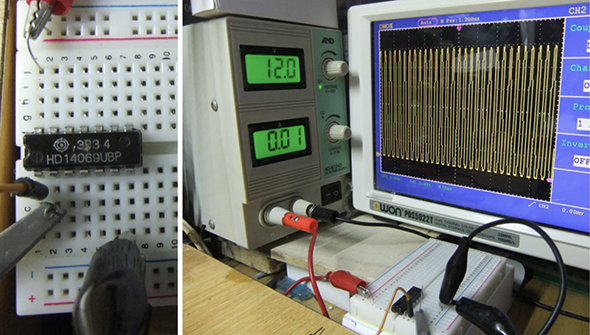

修理の依頼主へ回路変更を提案するため、CMOSロジックICの入力をオープンのまま放置すると危険であると依頼主に分かるような説明資料を作った。CMOSロジックICの消費電流と出力の波形を測定し、入力を処理した時とオープンにした時の違いが分かるように記載した。実験にはインバーターの「4069」を使用したが、図4は入力処理を0Vに接続した結果で、図5は入力端子をオープンにした結果の写真だ。

図4はCMOSロジックICの入力を0Vもしくは12Vに接続したもので、消費電力はほぼゼロで出力の12Vも安定している。

図5でCMOSロジックICの入力に10cmほどの配線をつないだ。入力をオープンにするとハムノイズ(60Hz)を拾い、出力波形にノイズ波形が出ることが分かる。消費電流は10mAが表示された。CMOSロジックICの出力に貫通電流が流れている。こうした事実を説明資料に記載し、依頼主にCMOSロジックICの入力端子を処理することの意味と重要性を理解してもらうことができた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング