デルタ-シグマADC内のノイズの概要:アナログ設計のきほん【ADCとノイズ】(1)(1/3 ページ)

デルタ-シグマADCのノイズに関する包括的な理解を深めるために、代表的なシグナルチェーンの一般的なノイズ源を調べ、ノイズを低減して高精度の測定を維持する手法を解説していきます。第1回は、ADCノイズの基本を重点的に見ていきながら、「ノイズとは何なのか」「高分解能ADCと低分解能ADCではノイズにどのような違いがあるか」などの疑問について、詳しく説明していきます。

シグナルチェーン設計における基本的な課題の一つが、アナログ−デジタル・コンバーター(以下、ADC)で対象とする信号を決定できるように、システムのノイズフロアを十分に低く抑えることです。消費電力の最小化、基板面積の縮小、コスト削減のための対策を行っていても、ノイズレベルが入力信号を上回れば、実質的にどのような設計も役に立たなくなります。つまり、シグナルチェーンノイズやそのアナログ−デジタル変換に対する影響および、その影響を最小限に抑える方法についての理解は、全てのアナログ設計者にとって基本的な知識といえます。

そのため、この連載「アナログ設計のきほん/ADCとノイズ編」では、デルタ-シグマADCのノイズに関する包括的な理解を提供することを目的としています。代表的なシグナルチェーンの一般的なノイズ源を調べ、ノイズを低減して高精度の測定を維持する手法を解説します。

本記事で取り上げるのは、正確度ではなく精度(ノイズ)であるという点です。この2つは区別なく用いられることの多い用語ですが、シグナルチェーン設計において関連はあるものの、別の側面を指しています。高性能データ収集システムを設計する際は、ノイズを最小限に抑えるだけでなく、オフセット、ゲイン誤差、積分非直線性(INL)、ドリフトなどの不正確度に起因する誤差を考慮することが必要です。

連載第1回(=今回)では、ADCノイズの基本を重点的に見ていきながら、以下のようなトピックに関する疑問に答えて、詳しく説明していきます。

- ノイズとは何なのか?

- 代表的なシグナルチェーンにおいてノイズはどこから発生するのか?

- ADC内の固有ノイズの把握

- 高分解能ADCと低分解能ADCではノイズにどのような違いがあるか?

第2回では、以下のトピックに焦点を移していきます。

- ADCノイズの測定

- ADCのデータシートにおけるノイズ仕様

- 絶対ノイズパラメーターと相対ノイズパラメーターの比較

第3回では、抵抗性ブリッジを使用した設計例の全体を段階的に見ていきながら、第1回と第2回で紹介する理論がどのように現実のアプリケーションに応用されているかを説明します。

ノイズとは何なのか?どこから発生するのか?

ノイズとは、期待される信号に加えて元の値から逸脱するような望ましくない信号(通常はランダム)です。ノイズは全ての電気システムに固有のものなので、「ノイズフリー」の回路は存在しません。

図1は、実際の世界でノイズがどのように発生するかを示しています。ノイズがフィルタリングされた画像と、フィルタリングされていない画像です。図1左の画像は細部が鮮明なのに対して、図1右の画像はほぼ完全にノイズに覆われています。図1の2つの画像がほとんど何の類似点もなくなっているのと同じように、アナログ−デジタル変換プロセスでは、アナログ入力とデジタル出力の間で情報が失われる結果になります。

電子回路内のノイズは、以下に示すような、さまざまな形で発生します。

- 広帯域ノイズ(熱ノイズ、ジョンソンノイズ):導電体内部の電荷の物理的な動きによって発生する温度依存のノイズ。

- 1/fノイズ(ピンクノイズ、フリッカノイズ):電力密度が周波数に反比例する低周波ノイズ。

- ポップコーンノイズ(バーストノイズ):低周波数の性質を持ち、デバイスの欠陥に起因するノイズ、発生がランダムで数学的な予測が不可能。

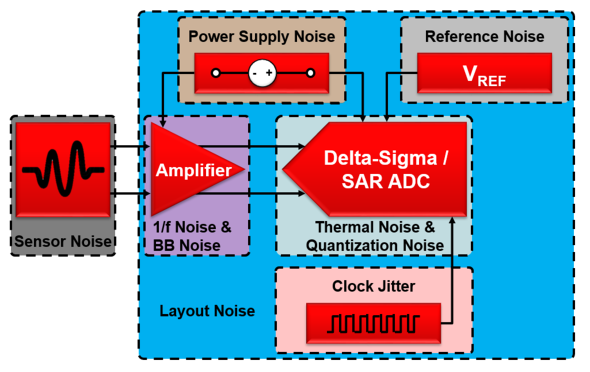

これらの形態のノイズは、以下に示す複数のノイズ源を介してシグナルチェーンに侵入します。

- ADC:熱ノイズと量子化ノイズからなる合成ノイズを発生。

- 内部または外部アンプ:広帯域ノイズと1/fノイズを発生させる場合があり、そのノイズがADCでサンプリングされて出力コード結果に影響を与える。

- 内部または外部電圧リファレンス:これも広帯域ノイズと1/fノイズを発生させ、そのノイズがADCの出力コードに反映。

- 理想的でない電源:測定しようとしている信号に複数の結合方法でノイズを付加する場合がある。

- 内部または外部クロック:不均一なサンプリングにつながるジッタを発生させます。これは正弦波入力信号に対する追加のノイズ源となり、一般に高速のADCほど重大な影響を受ける。

- 不適切なプリント配線板(PCB)レイアウト:システムまたは環境内の他の部品からのノイズを敏感なアナログ回路に結合することがある。

- センサー:高分解能システムにおいて最もノイズの多い部品となる可能性がある。

図2は、代表的な信号チェーンにおけるこれらのノイズ源を表しています。

連載第1回から第3回では、ADCの固有ノイズのみに焦点を絞って見ていきます。より包括的に理解できるように、残りの回路部品のノイズ源については、個別の記事で説明します。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:ノイズフリーの画像(左)とノイズのある同じ画像(右)

図1:ノイズフリーの画像(左)とノイズのある同じ画像(右) 図2:代表的なシグナルチェーンにおける一般的なノイズ源

図2:代表的なシグナルチェーンにおける一般的なノイズ源