ΔΣADC内ノイズの概要 ―― 本当に必要なノイズ特性は何かを探ってみる:アナログ設計のきほん【ADCとノイズ】(3)(2/4 ページ)

システムノイズパラメーターの定義

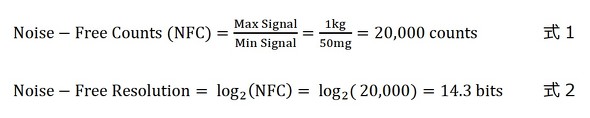

前回(第2回)では、システムノイズパラメーターの定義とADCの選択には、入力換算ノイズを使用することを推奨しました。ですが、今回は、ノイズフリーカウントとノイズフリー分解能を使用する、より一般的な方法から始めましょう。そうすれば、この方法と入力換算ノイズを直接使用する方法を比較できます。式1と式2では、初期ノイズパラメーターを計算します。

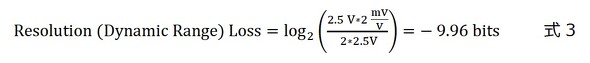

必要なノイズフリー分解能が14.3ビットの場合、16ビットADCで十分だと、すぐに判断してしまうかもしれません。しかし、第2回で述べたように、高分解能デルタ−シグマADCのノイズフリー分解能は、実際にはADCのフルスケール範囲のパーセンテージ使用率に左右されます。この例では、システムは2.5Vの基準電圧を使用し、最大入力信号は、励起電圧(2.5V)とブリッジ感度(2mV/V)の積です。式3に、第2回で示した式2を使用した予想分解能損失を示します。

これは驚くべき結果です。利用可能なフルスケール範囲の0.1%しか使用していないため、分解能をほぼ10ビットも失うことになります。このレベルでは、システム要件を満たすには24ビットADCでも不十分です。この問題を解決するには、システム仕様を変更するか入力信号を増幅するかして、パーセンテージ使用率を上げる必要があります。システム要件にはほとんどタッチできないと仮定すると、残された方法は入力ゲインを上げることです。それによって信号チェーンのノイズ特性が決定的に変化します。

幸いにも、増幅器のノイズがシステム性能にどのように影響するかを詳しく理解しなくても、分析を続けることができます。代わりに、これまでの知識を活用し、システム要件を満たすかどうかを判断するために、プログラマブルゲインアンプ(PGA)を内蔵したADCのデータシートのノイズ表を分析できます。

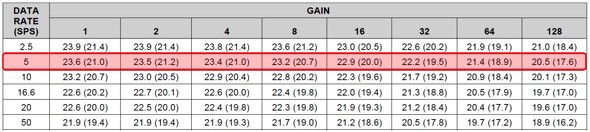

例えば、図2は、24ビットのADC『ADS124S08』の最大50SPSまでの有効分解能とノイズフリー分解能の表です。目標データレートは強調表示されています。このADCのゲインは1V/Vから最大128V/Vです。

このADCがシステム要件を満たすかどうかを判断するには、パーセンテージ使用率がゲインごとに異なることから、各ゲイン設定で別個に予想分解能損失を再計算する必要があります。そして、この結果を図2の対応するそれぞれのノイズフリー分解能値に加算し、システム仕様を満たすかどうかを確認する必要があります。表2に、ADS124S08を5SPSデータレートで使用したときの、算出されたシステムノイズフリー分解能(ビット単位)の一覧をまとめます。

| Data rate | Gain | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | |

| 5SPS | 11.03 | 12.23 | 13.03 | 13.73 | 14.03 | 14.53 | 14.93 | 14.63 |

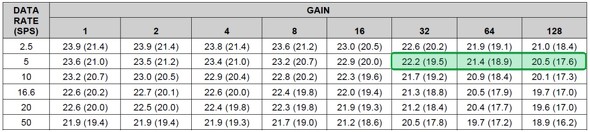

表2から、5SPSで32、64または128V/Vのゲインを使用した場合にのみ、必要なシステムノイズフリー分解能である14.3ビットを達成できることが分かります。図3は、これらの値を強調表示したデータシートのノイズ表です。

図3から分かる1つの重要なポイントは、計算をいくつも行わずにデータシートの値とシステムノイズパラメーターを結び付ける単純な方法はないということです。今は、結果が出ているので、このことはそれほど問題ないかもしれませんが、システム仕様が突然変更されたらどうなるでしょうか。

励起(基準)電圧を2.5Vから5Vに上げることにしたと仮定してください。ブリッジ感度も20mV/Vに増やすと仮定します(これは、最大ゲイン設定はADCの範囲を超えてしまうので使えないことを意味します)。また、5SPSではなく、20SPSでのサンプリングも検討しています。このような変更は、ADCノイズ分析にどのように影響するでしょうか。

この答えを出すには、新しいデータレートと基準電圧でのそれぞれのゲイン設定に対して分解能損失を計算し直さなくてはならないでしょう。さらに、5Vの基準電圧に基づいて図2の表を作り直さなければなりません。なぜなら、この表の計算には2.5Vの基準電圧が使われているからです。最後に、算出した分解能損失を、5Vの基準電圧を使って作成されたノイズフリー分解能の表から減算して、表2を作り直さなければなりません。

確かにこれは大変な作業です。その理由は、ノイズフリー分解能が相対パラメーターだからです。ここで、第2回で推奨したように絶対ノイズパラメーターの使用に切り替えて、分析の仕方がどう変わるか見てみましょう。

Copyright © ITmedia, Inc. All Rights Reserved.