信号の分解:デルタ-シグマADCでのアンプ・ノイズの影響:アナログ設計のきほん【ADCとノイズ】(6)(3/5 ページ)

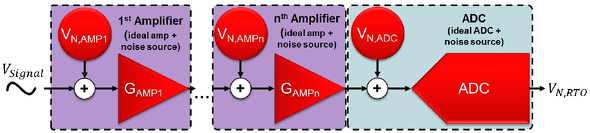

図5のように、シグナルチェーンにさらにアンプを追加したらどうなるでしょうか。ディスクリートのアンプを複数追加したり、アンプ内蔵や外付けアンプの付いたADCを追加したりすることもあるでしょう。

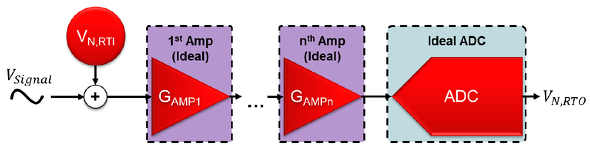

これらのノイズ項を全てまとめて1つの入力換算ノイズ源にした等価回路ノイズモデルを図6に示します。

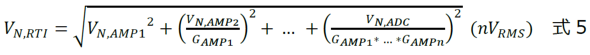

図6と式2および式3を用いて、式5に示すように、このようなn個のアンプがある拡張シグナルチェーンの入力換算ノイズを判定できるようになります。

前の例と同じく、新しい入力換算ノイズ式もシグナルチェーンの全デバイスからのノイズに依存します。しかし、各項は全てのアンプゲインの積の逆数で逓倍されますが、最初の項(最初のアンプの電圧ノイズ)だけはゲインと無関係です。

式4と同様に、1段目のゲインが大きい場合、式5のその他全ての項が事実上ゼロに近づくことになり、結果としてシステムの入力換算ノイズは1段目のアンプのノイズのみに依存することを意味します。そのため、単一段または複数段のアンプ構成で最良の性能を得るためには、1段目にゲインが大きい低ノイズアンプを選択してください。

式4で示すように、この選択が全てのADCで同じように効果があるわけではありません。実際に、低分解能のADCを高ノイズのアンプと組み合わせたり、より大きいゲインを利用しながら必要なシステムのノイズ特性を満たしたりもできるでしょう。その他にも、高分解能のADCではゲインがわずかに増加しても何の効果も感じられないかもしれません。

これらの結論を、16ビットの『ADS114S08』と24ビットの『ADS124S08』を比較して、さらに詳しく分析してみましょう。この2つのADCは、分解能は異なるものの、アンプノイズが同じプログラマブル・ゲイン・アンプ(PGA)を内蔵するなど、それ以外は同等です。この類似性のため、ADCの分解能の違いがゲインの変化によりシステムノイズにどう影響するかを分析することができます。

Copyright © ITmedia, Inc. All Rights Reserved.