デルタ-シグマADC使用時における電源ノイズ影響の低減:アナログ設計のきほん【ADCとノイズ】(最終回)(2/4 ページ)

PSRRの改善

それでは、システムのPSRRを良好に維持するいくつかの方法を、3つの異なる手法を使用して検討していきましょう。初めに、最も肝心なレイアウトについて説明します。

レイアウトの最適化

レイアウトの最適化は、PSRRの改善とシステム性能の維持に用いることができる、圧倒的に重要な手法です。電源に結合するDC/DCスイッチングレギュレーターのノイズについての説明を長々としてきた中で、実行可能なレイアウト最適化手段の1つが、影響を受けやすいアナログ入力からスイッチングレギュレーターを離して、このノイズを分離することです。スイッチングレギュレーターは効率が非常に高いものの、電源に注入される過渡事象が大きく、これが周りの回路やADC自体にも結合します。プリント配線板(PCB)の同じ面にデジタル部品と電源調整回路があれば、ノイズの多いリターン電流はどれも、より影響を受けやすいアナログ回路を流れずに済みます。

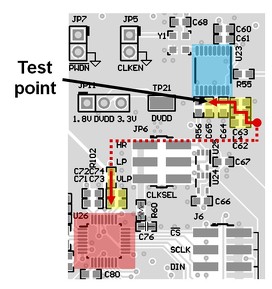

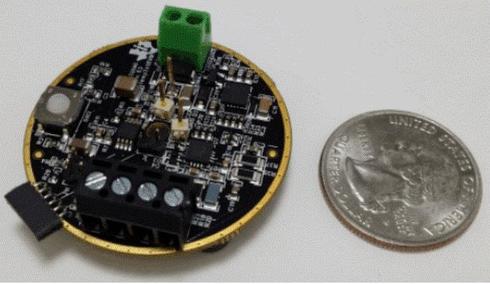

しかし、PCBによってはサイズや形状の制約が厳しく、このようなレイアウト手法が使えません。例えば、図6は、PCBのサイズを硬貨と比較したときの画像です(TIの温度トランスミッターのリファレンスデザインの1つ)。このように限られたスペースでは、レイアウトを最適化するのは困難でしょう。

このよう場合は(すべてのPCBレイアウトに言えることですが)、常に適切な電源デカップリングを使用するようにしてください。デカップリングコンデンサーは、大きくバルクとローカルの2つに分けられます。バルクデカップリングコンデンサーは、一般に電源の出力に直接配置されます。このコンデンサーは、電源の出力をフィルタリングし、負荷電流が変動しても安定した電圧を維持するのに役立ちます。それに加えて、ほとんどのアクティブ部品には、主電源ピンそれぞれのすぐ横にローカルデカップリングコンデンサーが少なくとも1個必要になります。ローカルコンデンサーは、一般にバルクコンデンサーに比べて容量が1桁小さく、高周波数ノイズをフィルターで除去しながら、デバイスからの瞬間的な電流要求に対応するのに使われます。特定の電源ピンにデカップリングコンデンサーを2つ以上(例えば0.01μFと1μFを並列で)使用することが推奨される場合は、小さい方のコンデンサーが電源ピンに近くなるように配置してください。

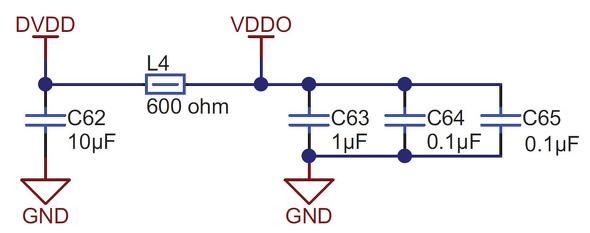

さらに、連載第11回では、クロックなどのある種のアクティブ部品から電源に、大きな過渡電流が流れる可能性があることを紹介しました。このノイズは、直列フェライトビーズといったデカップリング部品を追加することで抑えることができます。図7は、ADCとクロックファンアウトバッファ電源にデカップリング部品がいくつか追加された、ADS127L01EVMの回路図の一部です。このファンアウトバッファは、「ADS127L01」のデジタルコア(DVDD)と同じデジタル入出力レベルを基準としなければならず、このことでスイッチング過渡事象がこの電源に結合してしまうことがあります。システム性能を維持するために、EVMではコンデンサーとフェライトビーズを使って、ファンアウトバッファ出力電源(VDDO)からDVDDをデカップリングします。

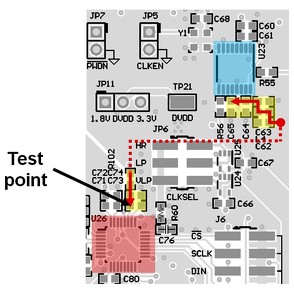

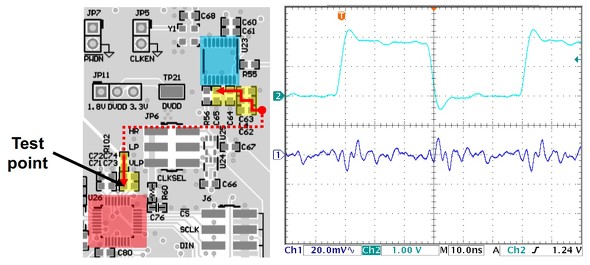

偶然にも、ADS127L01EVMのクロックファンアウトバッファとその一般的なクロック回路については、以前に連載第10回で触れました。そのときは、ファンアウトバッファを青で、ADCを赤で強調表示したEVMのクロック回路を紹介しました。図8の左図はそれと同じ図に同じように強調表示したものですが、今回はさらにデカップリング部品を黄色で、IOVDD電源へのDVDD電源パスを赤の矢印で示しています。

図8の左図に、IOVDD電源ピンのテストポイントを黒い矢印で示しています。右図は、このポイント(Ch1)の電圧のオシロスコープ画面をキャプチャしたものです。この画面キャプチャでは、C65における出力クロック信号(Ch2)の立ち上がりと立ち下がりのそれぞれのエッジで、バッファにより大きな電源過渡が生じているのが分かります。

図7に示したデカップリング回路がなければ、図8の右図に示される過渡事象がDVDDに結合し、図5で示した結果のように、ADCの性能に影響するでしょう。しかし、適切にデカップリングすることで、このようなグリッチをクロックファンアウトバッファの出力の中に封じ込めることができます。図9の左図に黒い矢印で示したテストポイント(C73)で、オシロスコープ画面をキャプチャした図9の右図を見ると、封じ込めの効果は明らかです。図8の過渡事象は、図9のキャプチャでは事実上取り除かれ、ADCまで到達する電源ノイズがほとんどなくなっていることに注目してください。

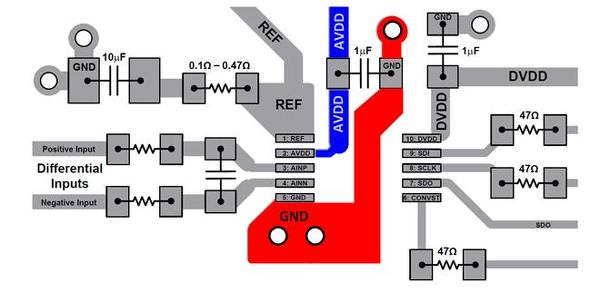

配線も、電源ノイズを低く維持するために検討すべき、もう1つのレイアウト手法です。可能な限り必ずソースからコンデンサーのパッドを通り、それからデバイスピンへと電源ラインを配線してください。また、大電流が流れる可能性がある電源には、幅広のパターンを使用します。そして、グランドも電源の1つであることも忘れないでください。グランドは、信号と電源の両方で、電流のリターンパスの働きをします。大きいグランド銅箔や余分なビアがあるプレーンを使用することで、リターンパスのインダクタンスが減少し、リターン電流がソースに戻る経路を見つけやすくなります。これらの考え方の一部を図10に示します。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図6:温度トランスミッターのPCBと硬貨の比較(TIDA-00095)

図6:温度トランスミッターのPCBと硬貨の比較(TIDA-00095) 図7:ADS127L01EVM回路図でのADCのデジタル電源(DVDD)とクロックバッファ出力電源(VDDO)のデカップリング部品(コンデンサーとフェライトビーズ)

図7:ADS127L01EVM回路図でのADCのデジタル電源(DVDD)とクロックバッファ出力電源(VDDO)のデカップリング部品(コンデンサーとフェライトビーズ)