構造化アセンブリを始めよう:複雑なSoC設計で導入すべき(1/2 ページ)

日々、複雑化するSoC(System-on-Chip)の設計。そうした中でSoC設計に「構造化アセンブリ」を導入することで、多くの課題を解決、回避できる。そこで、構造化アセンブリについて紹介する。

SoC(System-on-Chip)のトップレベルは、設計の残りの部分と同様、RTLで定義されます。歴史的にRTLはテキストエディタにて設計されてきました。しかしながら、数十年前あたりから大規模SoCにおけるこのタスクがまったく手に負えないほど複雑になり、今では大半のSoCでその限界を超えています。これはなぜなのでしょう? SoC内のIPの数の多さが一つの要因であることは明らかで、トップレベルでの接続数は爆発的に増えています。例えば、一つのAXIチャンネル接続が25個の信号を持っていることもあります。設計全般において複数のフレーバのAMBA-AMBA接続が急速に増えてきています。また設計者は、設計が進むにつれて進化していくトップインフラ――クロック、リセット、電力管理、テスト――も考慮に入れておかなければなりません。これらの要求事項により、ごく普通のSoCですら接続数が1万に達することもあります。IP間の接続には、複数のコンフィギュレーション・タイオフ・オプションを持つ、数百に及ぶポートが使用されているかもしれません。これらのポートは未接続のこともあれば接続されていることもあり、他にも考慮すべき重要な事柄は山ほどあります。図1に示すように、設計の小規模サブセットにおいてさえ典型的なインターコネクトの複雑さが相当なものであることは明らかです。

単一IPのインスタンス化が数百行にわたるようなレベルにおいて、人間がじかにRTLを書くことは不可能です。大規模SoCの設計チームがここ10年間で構造化アセンブリ方式に移行してきたのはそのためです。この方式でも出力がRTLトップレベル・ネットリストであることに変わりはありません。ですが、抽象化と自動化により、タスクの組み立て、改良、更新を大幅に簡素化するように設計されたツールと方法で構築されています。これらのツールはたいていIP-XACT規格に準じています。これは元々Accelleraによって開発されたXMLベースのフォーマットで、現在はIEEE 1685としてサポートされています。こちらの流れに乗ることには他にもさまざまな利点があります。例としては、SoCの完全かつ詳細なメモリマップの自動生成、メモリマップやクロックデータなどのドキュメンテーション挿入などがあります。これによりコンセプトからサインオフまでの追跡要件のトレーサビリティが確保されます。

SoCのアセンブリ

アセンブリタスクを簡素化する第1の鍵は、例えば一つのAXIバスが単一接続として扱われるような、バスプロトコルの抽象化にあります。IP-XACTではいくつかのプロトコルの標準定義が規定されています。これらは拡張することができ、新しいプロトコルまたはバンドルも定義することが可能です。そして第2の鍵は、インスタンス、ポート、接続、階層のスクリプト化可能な定義に基づく自動化にあります。スクリプトではRTL記述でよく見かけるものよりもリッチなプロパティセットを定義し、アクセスすることができます。例えば、インターフェースのマスタ/スレーブの種別や、ポートの信号タイプ(クロック、リセット、データなど)を含めることができます。本記事ではPythonで記述されたスクリプトの例を示します。プログラミング言語Tclもサポートされています。

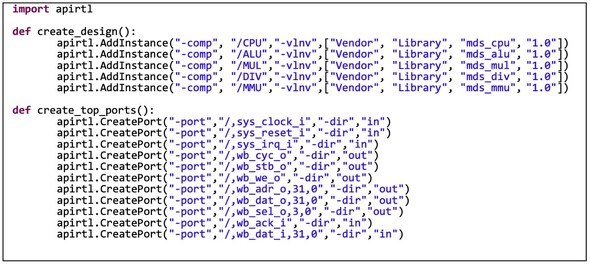

このプロセスは容易に理解できます。IPDプラットフォームで提供されているリッチAPIを使用することでオブジェクトの作成、削除、修正が行えます。プロパティにアクセスしてスクリプト作成をガイドすることもできます。図2は、CurrentDesignオブジェクトにインスタンスとポートを追加する単純なルーチンを示しています。

Pythonによる設計記述の組み込みは、強力なユーザー定義の自動化を可能にします。手続き的な定義に従う回路のあらゆる側面は、直接的なインスタンス記述や接続を用いて定義する代わりに、図2に示すような一つのプロシージャで自動化できます。SoCアセンブリにおける一般的なテクニックの一つに(特にIPのバスインターフェースを対応するバスファブリックインスタンスに接続する場合において)、connect-by-nameの使用があります。この接続の自動化の例を図3に示します。自動チェック機能によってもこのアセンブリプロセスを検証することができ、構成中にエラーを検出できます。このタスクを自動化するPython関数の定義は非常に簡単です。もっと複雑な例としては、パワーマネジメント機構のインスタンスおよび、接続が挙げられます。これもまたプロシージャで自動化することが可能な、十分に定義されているものの複雑な手続きのうちの一つです。最も重要なことは、これらのプロシージャは適切にデバッグされてさえいれば、設計が進化しようと、あるいは設計ファミリ全体においてさえ、変える必要がないということです。プロシージャを使用した自動化により、SoCアセンブリの段階から機能的な複雑さをかなり抽象化できます。

Copyright © ITmedia, Inc. All Rights Reserved.