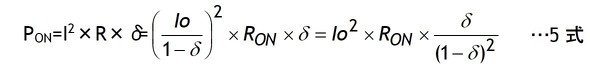

ステップアップ形DC/DCコンバーターの設計(2)使用する部品の定格:たった2つの式で始めるDC/DCコンバーターの設計(9)(2/4 ページ)

半導体の温度計算

このように計算に従ってDC/DCコンバーターの設計を進めていく中で半導体の電圧、電流定格以外で問題になるのが前回シリーズでも説明した半導体の温度定格です。

温度計算をする意味は既にステップダウンコンバーターの章で説明しましたが温度は半導体自身の信頼性を左右すると同時にはんだ付けの故障率や信頼性に影響します。

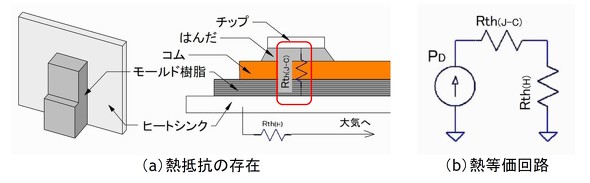

実際のDC/DCコンバーターにおいて半導体はヒートシンクに図3(a)のように取り付けられ、スイッチング動作などでFETチップなどに発生した損失は熱となってヒートシンクを介して空気中に拡散します。この様子を電気回路として表したものが図3(b)の回路であり、式で表すと4式になります。

ここで各記号の意味は次の通りです。

| P | 損失(W) |

|---|---|

| Rth(J-C) | ジャンクション〜ケース間熱抵抗(℃/W) |

| Rth(H) | ヒートシンク熱抵抗(℃/W) |

図3や4式を見れば損失P(W)とヒートシンク熱抵抗Rth(H)(℃/W)が設計者として検討できることが分かります。

最初の手順としてこの4式のΔT以下になるように設計者はヒートシンクの材質、形状、表面処理などを選定します。もう一つの設計因子の損失Pはスイッチング動作によるもの(PSW)とRONによるもの(PON)に分類できます。

発生した損失Pと許容されるチップの温度上昇から熱抵抗Rth(H)の最大値が決まります。このチップの温度は半導体素子のはんだの温度を左右し、はんだの故障率や信頼性に影響します。

この観点からはんだ温度は90℃以下に抑えたいのでリードや端子部の温度は90℃とします。ですから機器内の最高温度を50℃とすれば許される温度上昇は40℃以内にしなければなりません。つまり40/P(℃/W)以下の熱抵抗を持つヒートシンクを使用することになります(厳密にはRth(J-C)を考慮)。

※近年では設計者がディスクリート部品でDC/DCコンバーターを個別に設計するよりもソリッド化した1つの部品としてのDC/DCコンバーターを購入し、回路に配置することもあるかと思います。

ですがその場合でも損失(熱)は発生しますのでこのような放熱設計は必要になります。

RON:FETのオン抵抗です。

FETはオン時に抵抗性の物性を示します。FET(M1)がオンしている時、ドレインにはFETのオン抵抗RONに起因する次のようなジュール損が発生します。ここで使用する電流波形や記号は図6によるものとします。

FET(M1)にはton中だけIo/(1−δ)の平均電流が流れ、この電流に加えてチョークの励磁電流ΔIが流れます。ですが励磁電流ΔIは平均値に対してマイナス域からプラス域の変化をしますので損失に与える影響は打ち消し合って減少し、主として平均値が損失を左右します。したがってPONは次の5式で表すことができます。

出力電流Ioは定電圧制御が機能している限り一定なので通電時比率δが損失を左右します。その結果、

・低入力:δ→大→PON大

・高入力:δ→小→PON小

となり、低入力時ほどPONは増加します。

5式からチップサイズを大きくすればRONが小さくなりPONは減少しますがチップサイズが大きくなれば寄生容量も増加するのでPSWが増加します。またPSWはFETの動作がオン/オフを繰り返すたびに発生するので動作周波数に比例して増加します。したがって損失Pは周波数依存性を持つことになり同じ電気定格でも動作周波数ごとに最適チップサイズは異なってきます。実際に最適チップサイズを求めるにはRON別に損失を測定し比較する必要があります。

ですから前モデルの設計をそのまま踏襲して動作周波数のみを変更すると思わぬ損失増加になる場合もあるので設計仕様の変更には注意が必要です。

Copyright © ITmedia, Inc. All Rights Reserved.

図3:FETの放熱図

図3:FETの放熱図