チップ設計にAIを TSMCとEDAベンダーの協業が加速:Cadence、Synopsys、Siemensが続々投入(1/2 ページ)

チップ設計におけるAI(人工知能)の活用が活発になっている。Cadence Design Systems、Synopsys、Siemens EDAの大手EDAツールメーカー3社は、TSMCとの連携をさらに強め、AIを活用してチップの設計や検証を加速するツールを開発している。

半導体設計と製造において、AI(人工知能)の活用は着実に広がりつつある。それは、大手EDAベンダーとシリコンファウンドリーの協業からも見て取れる。Cadence Design Systems、Synopsys、Siemens EDAの大手EDAツールメーカー3社は最近、TSMCの先進チップ製造ノード向けAI駆動型設計フローにおいて緊密に連携することを発表した。

半導体工場は、先進の製造ノードにおける光学的近接補正のための正確なリソグラフィモデルを備えなければならない。IBM Researchのグローバル半導体研究開発およびアルバニーオペレーション担当バイスプレジデントを務めるHuiming Bu氏は、「AI/機械学習を活用することで、シリコン製造時に最良の結果をもたらす高精度モデルの開発が加速する」と述べている。

設計面では、AIを活用したEDAソフトウェアで複雑なIC設計の最適化を支援すると同時に、2D(次元)/3Dマルチダイアーキテクチャへの移行を促進している。Synopsys EDA Groupのジェネラルマネジャーを務めるShankar Krishnamoorthy氏は、「複雑さの増大やエンジニアリングリソースの制約、納期の厳格化などの課題によって、アーキテクチャの検討から設計、製造までを網羅するAI駆動型の完全なEDAソフトウェアスタックが求められている」と述べる。

以下では、先進プロセスノード向けAI駆動設計フローを中心とした、EDAツールメーカー各社とTSMCとの現在の連携について簡単に紹介する。

生成AIを採用したCadenceの設計プラットフォーム

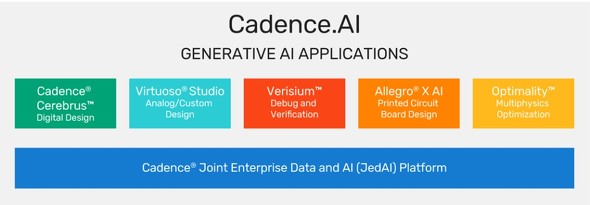

Cadence Design Systemsは、TSMCと連携しAIプラットフォーム「Cadence.AI」を開発している。Cadence.AIは、チップからシステムまでの設計と検証のあらゆる側面に対応し、AIツールを使用したデジタルおよびアナログ設計の自動化を促進する。両社は、設計のデバッグと解析に生成AIを採用した「Cadence Joint Enterprise Data and AI (JedAI) Platform」に関しても協力している。

Copyright © ITmedia, Inc. All Rights Reserved.