arm vs RISC-V!主要MCUの特徴と性能を徹底比較:知っておきたい主要MCU(2/3 ページ)

2. 主要なMCUコアの機能・性能比較

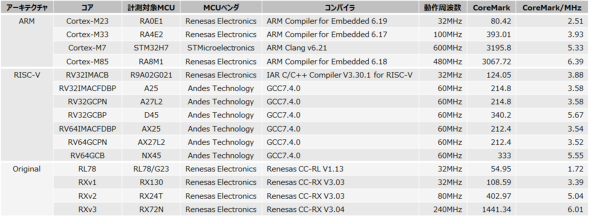

CoreMarkベンチマーク

EEMBCで公開されているCoreMarkのベンチマーク結果を見てみましょう。

どのアーキテクチャも基本的にはコアの世代、ランクが上がると周波数あたりの性能(CoreMark/MHz)が上がっているのが分かります。

RISC-Vは同名のコアでのIPとして固まったものではなく、各社がIPへの実装を工夫するため、同名コア(同じExtensionを盛り込んだもの)でも実装により性能が変わります。Andes Technologyでは20番台は5-stage、40番台は8-stageとなるため、性能差が出ています。

※RISC-Vのコア名(Extension)に関しては、この後説明します。

arm

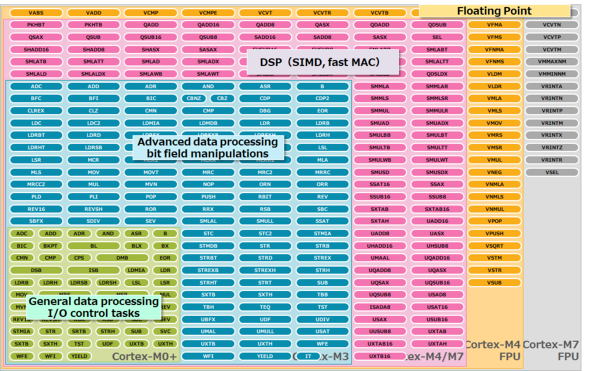

現在、ARMのMCUコアはARMv6-MからARMv8.1-Mまでを展開しています。

ARMv6-MからARMv7-Mまではスケーラブルに命令セットを拡張する形で、Cortex-M0/M0+からM7まで製品展開しています。

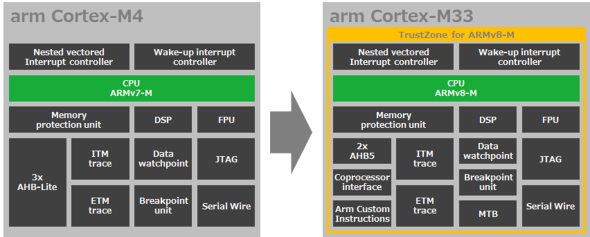

ARMv7-MからARMv8-Mの変化は、Cortex-M4とCortex-M33を例に見ると、TrustZone対応とMTB(Micro Trace Buffer)であることが分かります。

IoT化が進む中、機器のセキュリティ対応が必要となっていますが、ARMv8-MではTrustZoneによりセキュリティの強化を図っています。

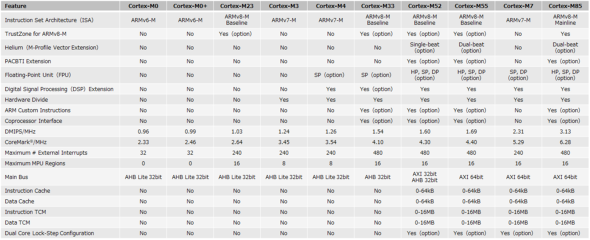

細かな構成差分は下表をご参照ください。

RISC-V

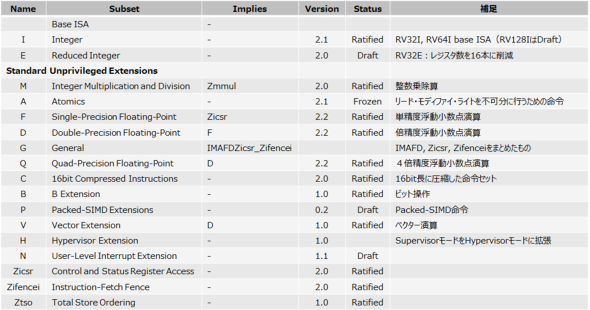

Base ISAであるRV32I, RV64I, RV32Eを基本として、下表に示す拡張命令セット(Extension)を付加することでMCUコアでサポートするISAを決定します。拡張命令セットの組み合わせにより、アプリケーションで必要となる機能を実現します。

また、RISC-Vコアの名称は下表のExtensionで対応しているもののNameを上から順に記載するものとなります。

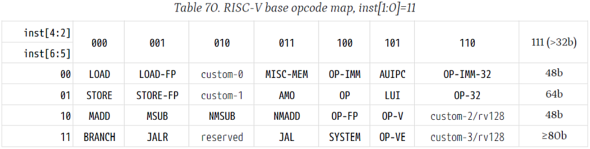

RISC-VのオペコードマップにはCustom0〜3があり、カスタム命令として独自の命令を実装することが可能です。MCUコアベンダーがアプリケーションに合わせた命令を実装することで、アプリケーションの処理速度を向上させることができます。

Copyright © Ryoyo Ryosan, Inc. All rights reserved.

記事ランキング