高インピーダンスセンサーの信号処理法(2/3 ページ)

デバイスとアンプに関する考察

個々のMOS FETは、リーク電流の仕様上の性能はあまりよくないが、実際には仕様よりも6桁も性能がよい場合がある。例えば、よく使われる2N7002は、仕様では最大チャンネルリーク電流1mA、ゲートリーク電流0.1mAとなっている。しかし、実験室で、ドレイン、接地ゲート、およびソースを20Vにして、これらのデバイスを見てみると、総リーク電流はわずか1pAであることがわかる。明らかに、仕様が実際の特性に基づいたものではなく、生産テスト時間のコストに制約されている。より正確な仕様を示すためには、より長いテスト時間とよりよいテスト装置が必要となり、これにはコストがかかる。また、正確に仕様を示そうとすると、多くの場合生産数は減ってしまうため、その代償も大きい。

超低リーク電流マッチドペアJFETには、米Linear Integrated Systems社(www.linearsystems.com)の「LS 830」、および米InterFET社(www.interfet.com)の「IFN124」がある。人気のあるJFETは、蘭Philips社(www.semiconductors.philips.com)の「BF862」である。これは、ゲート電流が3pA、ノイズ密度がサブナノボルト以下で、ピンチオフ電圧が0.6Vと扱いやすい。2N4416もまた、特にそのpF以下の入力静電容量とノイズ密度がよい点から、人気があるが、JFETのピンチオフ電圧は2Vから6Vと変動も値も大きいため、それを嫌う設計者は多い。

CMOSオペアンプはもう何年も存在するが、仕様はあまり高くなく、実際の性能はそれ以下である。Linear Technology社は高精度マイクロパワー「LTC6078」、およびより高速な「LTC 6241」CMOSオペアンプを最近発表した。LTC6241の代表的な入力リーク電流は70℃で4pAという値である。JFET入力ベースの電位計グレードのオペアンプはもう何年も前から市場に存在するが、その価格は比較的高い。つまるところ、どのオペアンプも半導体デバイスも完璧ではなく、設計者がリレーや較正やチョッピング技術を駆使して最良の直流結果を達成する方法を探るのである。

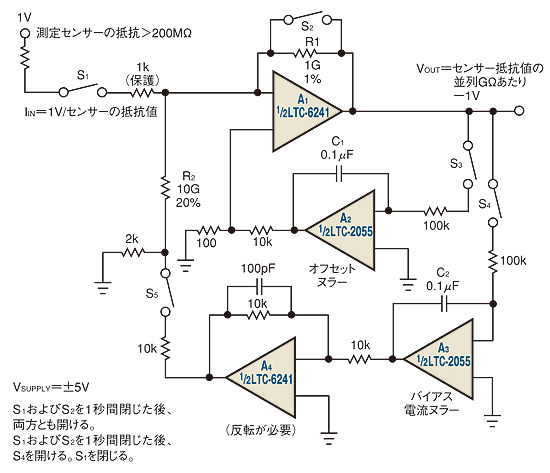

図1の回路は、2つの力の平衡ヌリング法を利用している。この動作をたどるために、すべてのスイッチが開いた状態からS2およびS3を閉じるとする。これにより、超高精度集積アンプA2を駆動し、A1の出力をグラウンドに短絡する。A1の入力オフセットは、その正の入力に現れ、C1がこのオフセットの101倍を蓄積する。S3を開くと、A1は再び正常に動作するが、実効オフセットは1mVで、約1mV/秒のドリフトがある。ここで、S2を開くとフィードバック抵抗R1が回路に加わり、出力電圧はIBIAS×R1に等しくなり、通常その値は1mVである。S4およびS5を閉じると、A1の出力は再びゼロとなるが、今回はA3を通る。A1のバイアス電流がここでR2を通り、C2がそれを60 mV/pAの電圧として蓄積する。S4を開くとヌリング過程は終了する。

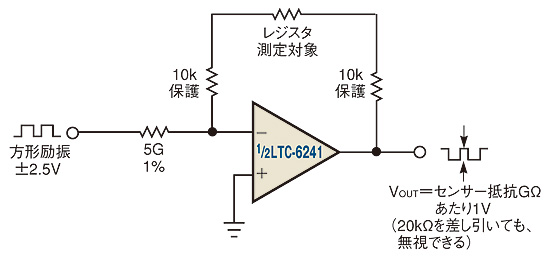

S1を閉じると、入力ドライブ、つまり測定対象の抵抗と、電圧源が接続される。アンプはほとんど完璧であるが、それほど長時間はもたない。コンデンサC1およびC2のドリフトは数秒もすると、またヌリング過程を必要とする。さもなければ、アンプの仕様は、何も手を加えていないLTC6241以下になってしまう。図2には、より簡単な方法を示す。アンプを完璧にするのではなく、この回路ではアンプの寄与を減少させるために励振をチョッピングする。また、ここでは測定対象の抵抗はフィードバック経路にあるので、出力は抵抗のアドミタンスではなく抵抗値に比例する。立ち上がり時間は、1GΩ抵抗で10ms(10〜90%)なので、励振は約10Hz以下で、適切に設定することができる。

図2 励振をチョッピングする技術により同等の精度をより簡単に得ることができる。アンプの特性を改善はしないが、測定し減少させる。オペアンプのオフセットとバイアス電流がいくらであるかなどは、あまり関係ない。

図2 励振をチョッピングする技術により同等の精度をより簡単に得ることができる。アンプの特性を改善はしないが、測定し減少させる。オペアンプのオフセットとバイアス電流がいくらであるかなどは、あまり関係ない。高インピーダンス回路を保護する

高Z回路を、入力インピーダンスに影響を及ぼすことなく保護するにはどうすればよいのだろうか? 厳密に言えば、それは不可能である。しかし、それに近づけることはできる。最善の方法の1つは、配線は少し長くなるが、直列抵抗といくつかの直列インダクタンスを使用することである。インダクタンスと寄生素子は、ESD(electrostatic discharge)パルスを分散させ、敏感なものに影響を及ぼす前に、それを外へ逃がしやすくする。影響を受けやすいコネクタピン周りのレイアウトにスパークギャップを設けることで、さらに逃がしやすくする。この手法は、安価で効果的であるが、高密度デジタル設計においては問題となる場合がある。スパークギャップは、強いEMI(electromagnetic interference)波を再放射し、不気味な青色も発する。この現象によりボード上の離れたところに配置されている486マイクロプロセッサが何度も破壊されたが、幸いなことにハードウエアを破損することはなかった。その設計にどれだけの強度を求めるかによって、必要な保護は異なる。この場合は、PCリセットを介入させたくなかったので、スパークギャップは失敗であったことになる。アナログ設計や簡単なデジタル設計においては、スパークギャップは問題にならないはずである。ガス放電管も部品として提供されており、同じ効果が得られる。

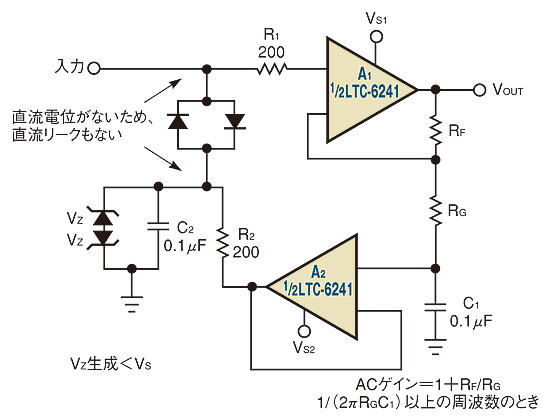

ダイオードクランプはほとんど必ずリークが生じる。ショットキー・ダイオードは、さらにリークが多いので、問題外である。超低リークダイオードには、米Central Semiconductor社(www.centralsemi.com)の「CMPD6001」、および蘭Philips社(www.semiconductors.philips.com)の「BAS416」がある。最大リーク電流の仕様は、デバイスが冷たい状態でも500pAから5nAである。高温の場合の仕様はさらに悪く、μA程度になることもよくある。最小リーク電流の性能に関しても、まだJFET接合の方がダイオードよりもよい。Vishay社がSOT-23パッケージで提供する「2N4393」は、リーク電流が室温で通常5pA、100℃で3nAである(図3)。このリーク電流を、LTC6241の70℃で75pAという最大バイアス電流の仕様と比較してみよう。リーク電流の低いダイオードを加えても、そのリーク電流はかなり悪くなる。しかし、設計方法によりこの問題を補うことができる。例えば、トラッキングリミッタ回路(図3)を考えてみる。A2はダイオードに逆バイアスをかけ、C1は平均直流電圧を蓄積する。このシステムは、蓄積コンデンサの過電圧とスパイクを抑えるが、ユニティゲインで直流を通すため、入力を保護し、入力の過負荷回復時間を改善する。直流ゲインに対しては、単にC1を短絡させ、入力をA2からA1の反転入力に変えるとよい。反転回路を保護するのはより簡単で、ダイオードをグラウンドに接続するだけでよい。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 ヌリング法は魅力的だが、それを利用するにはかなりの努力とシールド技術が必要となる。このような「完璧な」アンプを作成するのはコストがかかり、信頼性の高い堅固な設計という目的からははずれてしまう。

図1 ヌリング法は魅力的だが、それを利用するにはかなりの努力とシールド技術が必要となる。このような「完璧な」アンプを作成するのはコストがかかり、信頼性の高い堅固な設計という目的からははずれてしまう。 図3 トラッキングクランプには保護ダイオードがあるが、A2がそれらを入力と同電圧に逆駆動する。ツェナーダイオードとそのコンデンサが、クランプ電流の大部分を保持する。Rv1およびR2が電流をアンプに流さない。

図3 トラッキングクランプには保護ダイオードがあるが、A2がそれらを入力と同電圧に逆駆動する。ツェナーダイオードとそのコンデンサが、クランプ電流の大部分を保持する。Rv1およびR2が電流をアンプに流さない。