システム開発にもエミュレータ――ソフト/ハードの並行開発を実現(2/2 ページ)

システム開発におけるハードウエア・エミュレーション

ISSモデル、TLM、純粋なCまたはC++モデルはいずれも、設計の分割に向けた基本システムアーキテクチャの評価手段を、システム開発者に提供するが、時間領域における解析をサポートする機能がない。これらのモデルには、意図的にタイミングモデルがない。その開発の主な目的が、シミュレーションのスループットをできる限り速くすることだからである。しかし、ほとんどの組み込みソフトウエアは時間に依存して動作し、種々のハードウエアブロック間においては時間の同期が必要となる。これらタイミングを検証するのにRTLデータを待たなければならないとすれば、使い物にならない。RTLを用いたシミュレーションは、抽象モデルを用いる場合よりも著しく遅い。その結果、ソフトウエアの検証にかなりの時間がかかってしまい、開発時間が増大する。すると、NRE(nonrecurring engineering)コストが増大し、さらには製品が市場投入時期に間に合わない可能性すら生じるのだ。

EDAベンダーは、回路をハードウエア・プリミティブにコンパイルするハードウエア・アクセラレータを作成し、スループットの問題に対処している。米Cadence社(http://www.cadence.com)、米Mentor社(http://www.mentor.com)、米Tharas Systems社(http://www.tharas.com)といったベンダーが、ハードウエア・アクセラレータを販売しているが、それらは実行速度は十分なものの、かなり高価である。このようなハードウエアブロックにより、論理シミュレータのゲートレベルのスループットは1000倍も速くなるが、その価格は数100万米ドルにものぼり、多くの企業にとって手の届かない製品である。

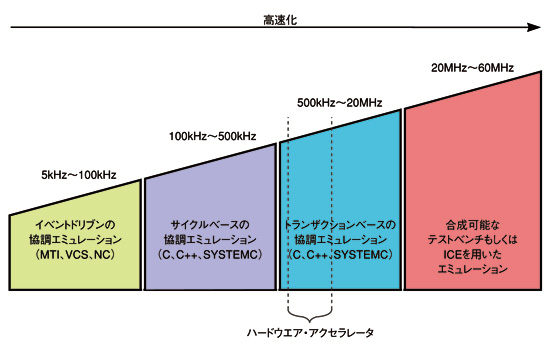

図1は、種々のシミュレーション手法を適用した場合のシミュレーション性能の改善を示したものである。ハードウエア・アクセラレーションにより、イベントドリブンのシミュレーションは改善され、そのスループットはトランザクションベースのコ・エミュレーションに届くまでとなった。ハードウエア・アクセラレータは、リグレッションテストに使用すると、生産性向上に最も貢献するといえる。

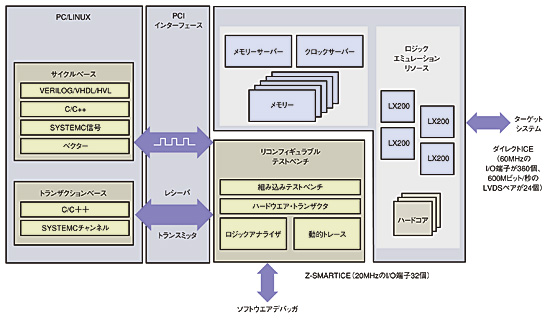

もう1つの手法は、ハードウエア・エミュレータを使用する方法である。エミュレータを使用すれば、ASICの代わりにFPGAを用いて回路の実装および検証が可能になるため、シミュレーションのスループットは、ソフトウエア・シミュレータを用いた場合よりもずっと高い。エミュレータが最初に出現した頃は、すべての回路がFPGAに実装されていなければならなかったが、今日のエミュレータはソフトウエア・シミュレータと通信することが可能で、ソフトウエア・シミュレータがサポートするモデルならば使用することができるようになった。エミュレータの能力もかなり向上した。図2は、仏EVE社(http://www.eve-usa.com)の最新エミュレータであるZebu-UFのアーキテクチャを示したものである。システム開発者は、エミュレータの能力を利用して、さまざまな検証を行うことができる。

IP市場の成長を妨げている要因の1つとして、潜在的なユーザーは、ベンダーと契約を交わさない限りIPコアを評価できないという点が挙げられる。コアのTLMを使うのは効率的ではない。IPベンダーはモデルを開発し、保守する必要がある。ベンダーはIPを開発するために内部的に使用したモデルを配布することはできない。評価モデルの目的が、内部的に開発されたモデルとは異なるからである。市販のTLMのアーキテクチャに疎い設計者でも容易に使用できるものとしなければならない。高速なシミュレーションを可能とするために十分に抽象化されていなければならず、また、コアの機能を正確に表していなければならない。コアをエミュレータボードに差し込むことで、残りのシステムのアーキテクチャ記述を用いた評価を実行できるならば、顧客の要求を満たしているといえよう。その一方でベンダーは、マーケティングコストを削減し、IP保護を強化している。

四半世紀ほど前には、設計チームが開発システムを利用せずにマイクロプロセッサのためのソフトウエアを開発することはなかった。これらのシステムは各ベンダーに固有であり、ほとんどの場合は1つのマイクロプロセッサに固有であった。エミュレータの主な利点はその柔軟性である。図2に示すように、ソフトウエア検証は英ARM社(http://www.arm.com)、英ARC社(http://www.arc.com)、または米Tensilica社(http://www.tensilica.com)の開発環境を接続して実行でき、リアルタイムでソフトウエアをデバッグしたり、システムの残りの部分を種々の抽象度でモデル化したりできる。この機能により、ハードウエアとソフトウエアの開発を真に並列化することが可能となり、開発サイクルを短縮するだけでなく、ハードウエアとソフトウエア実装のトレードオフが早い段階で可能となるため、製品全体としての品質が向上することになる。

ワークステーションとZebu-UFのようなエミュレータを利用することで、Tensilica社が提供しているような再構成可能なプロセッサの命令セットをカスタマイズして組み込みソフトウエアの開発およびデバッグを行い、サードパーティIPを評価することができる。また、各ブロックの抽象モデルに関わらず、設計全体に常時アクセスできる環境で回路をデバッグすることも可能である。モデルとしてさまざまな抽象度を使用できる機能により、製品のアーキテクチャ決定をできる限り先送りにすることができ、その間にブロックの一部を開発することも可能である。ソフトウエアも含めてシステム全体を、適切なスループットでシミュレーションできる。

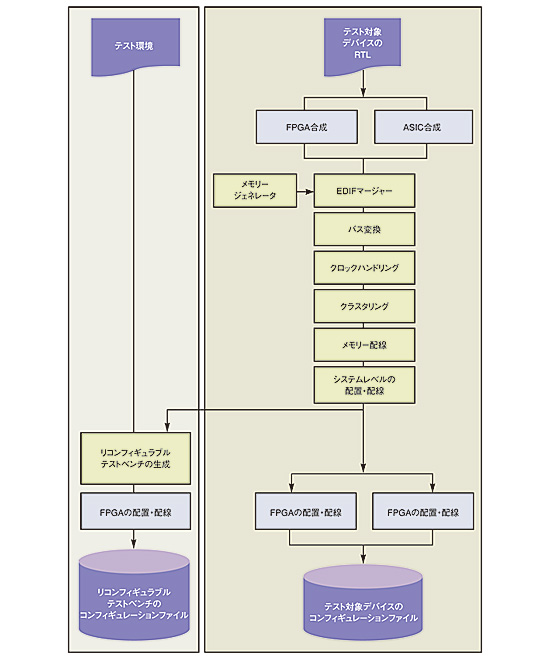

コンパイル速度は、初期のエミュレータの欠点の1つであった。エミュレーションのために設計をコンパイルするには、合成、分割、および配置配線ツールが必要である(図3)。回路が大きくなると、これらの機能も急激に増大する。デバッグ実行の間に何時間も待たなければならないとすれば、生産性に深刻な影響を及ぼすことになる。エミュレータおよびハードウエア・アクセラレータのベンダーは、回路のインクリメンタル・コンパイルを実現して、回路の大部分に変更がない場合には変更部分のみの再コンパイルで対応できるようにした。

早い段階でハードウエア実装に着手できることは、特に組み込みソフトウエアの開発者にとっては非常に有用である。組み込みソフトウエアはタイミングと割り込みに依存するが、それらを両方ともサポートするESLツールはない。従来のプログラミングおよびモデリング言語であるC、C++、SystemC、およびJavaでさえも、時間または割り込みのメカニズムをサポートしていない*1)。このため、ソフトウエア設計者は論理シミュレータを使用して作業を完了することはできず、実際のハードウエアに依存せざるを得ない。エミュレータは初期から、リアルタイム・ソフトウエアのデバッグをサポートしている。

システム開発者はシステムの残りの部分のTLMを利用でき、一方、エミュレータはシステムの一部分のゲートレベル実装をサポートする。種々のブロック間の通信パターンを調査して、ブロック分割を再調整し、バストラフィックを最小化するためにハードウエアからソフトウエア、またはその逆に、機能の実装を変更することができる。システムの残りの部分をシミュレーションするのにどのモデリング言語を使用しても、エミュレータを利用することができる。

LSIをシステムとみなす開発者は非常に多い。にも関わらず、すべてのLSIを基板上に実装する必要があり、開発者はシステムのパラメータを決定するのに、パッケージと基板の両方の影響を考慮しなければならない。設計者は、設計を製造にまわす前に、ICE(in circuit emulator)を用いて、LSIのみではなく製品全体の動作を確認することができる。ICEにより、システム開発者は設計を最終的に決定するずっと前に、製品全体をシミュレーションすることができ、設計のやり直しが発生する確率は減少する。設計者が、設計実装の最終段階のデバッグとリグレッションテストのためだけに使用していたエミュレータが、今やシステム開発者にとっても有用なツールとなったのである。

脚注

※1…Lee, Edward E, "Absolutely Positively on Time: What Would It Take?" IEEE Computer, July 2005, pg 85.

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図1 より抽象度の高いモデル、ハードウエアアクセラレータ、エミュレータを使うことで論理シミュレーションは高速化できる。

図1 より抽象度の高いモデル、ハードウエアアクセラレータ、エミュレータを使うことで論理シミュレーションは高速化できる。 図2 最新のエミュレータは、IPの評価、論理シミュレーション、組み込みソフトウエアのデバッグ、およびICEに対応している。そしてこれらは従来の論理シミュレーションと統合可能である。

図2 最新のエミュレータは、IPの評価、論理シミュレーション、組み込みソフトウエアのデバッグ、およびICEに対応している。そしてこれらは従来の論理シミュレーションと統合可能である。 図3 設計したハードウエア、ソフトウエア、およびテストベンチのエミュレータへのマッピング処理は膨大な時間を要する。ツールベンダーは、インクリメンタルコンパイルの実現によって、処理を軽減している。

図3 設計したハードウエア、ソフトウエア、およびテストベンチのエミュレータへのマッピング処理は膨大な時間を要する。ツールベンダーは、インクリメンタルコンパイルの実現によって、処理を軽減している。