ターミネータI:Signal Integrity

私の友人であるLloyd氏は、高エネルギー物理学実験のためのタイミング・アナライザを作成している。この種の実験では、何百もの検知器を配列したアレイを使って、連鎖的に起こる原子間の相互作用により粒子の噴霧を発生させ、その粒子が到達するまでの時間を検知する。

各検知器が、長さの等しい同軸ケーブルを介してLloyd氏のアナライザに接続される。アナライザは、各原子の到達時間データを記録し、その位置を三角測量する。較正されていれば、システムの精度は非常に高い。

検知器は、アナライザから3フィート(約0.9m)離れた高放射領域に設置される。この距離でRG-58A/U 50Ω同軸ケーブルを使うと、検知器出力の立ち上がり時間400psを若干遅くするかもしれない。しかし、各検知器へのケーブルの影響が同じで、ケーブル自体のステップ応答が深刻なジッターを加えないのならば、問題はない(実際にはそのようなことはない)。

検知器出力とアナライザ入力の間に反射が生じると、それは問題である。遅延のある反射が生じると、反射信号により、後続の事象の立ち上がりエッジがあいまいになり、その到達時刻が実際よりもずれて見えてしまう可能性がある。このメカニズムにより生じるジッターを、システムから後処理で除去することはできない。

反射の振幅を、例えば信号振幅のχ% に制限することができるとすると、この誤った反射により生じる時間領域ジッターは、最悪の場合でも、信号の立ち上がり時間のわずかχ%となる。

ここで、読者は両端を終端すれば良いと考えていることだろう。終端は、反射を緩和する非常によい方法である。しかし、例えばここで、「検知器は政府の請負業者が作成したもので、低インピーダンスECL出力を持つ」としてみよう。それならば変更することはできない。つまりこの場合には、アナライザがほとんど完璧な終端を提供する必要がある。

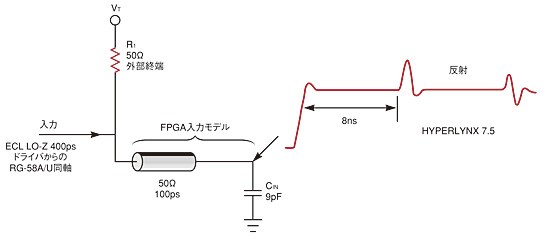

次に、コスト上の理由から、検出信号を受信するのに在庫にあるFPGAを使わなければならないとする。FPGAは切り替えが可能な内部抵抗を内蔵するが、それらはこのアプリケーションに十分なほど精度が良くない。各信号に対して50Ω±1%の外部終端抵抗を使用することが要求されている。

残念なことに、完璧な外部終端があっても、FPGAの入力容量9pFにより、大きな反射が生じてしまう(図1)。反射は、同軸ケーブルの往復遅延に相当する、8nsごとに返ってくる。システム仕様を作成した人はこの事実を考慮し忘れたようである。

どのようなシステムでも、時間定数1/2・Z0CINがソースの立ち上がり時間に近づくと、このような大きな反射が生じる。

さて、以上のように与えられた仕様で、Lloyd氏のシステムはうまく動作するのだろうか? その結果については、次回のコラムで解説するので、どうぞお楽しみに。

<筆者紹介>

Howard Johnson

Howard Johnson氏はSignal Consultingの学術博士。Oxford大学などで、デジタル・エンジニアを対象にしたテクニカル・ワークショップを頻繁に開催している。ご意見は次の電子メールアドレスまで。www.sigcon.comまたはhowie03@sigcon.com。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 FPGA-入力の容量により、大きな反射が生じる

図1 FPGA-入力の容量により、大きな反射が生じる