電源サブシステム入門:各方式の課題を再確認!(4/4 ページ)

AC-DCコンバータ

続いて、AC電圧からDC電圧を生成するAC-DCコンバータを取り上げる。AC電圧としては一般に屋内のAC電力線が使用され、この種のコンバータはオフライン電源と呼ばれることもある。ほかに、既存の整流回路からのDC電圧を入力とし、絶縁トポロジを用いてDC電圧を生成するものもある。伊仏合弁のSTMicroelectronics社、米Allegro MicroSystems社、ON Semiconductor社、Power Integrations社、Texas Instruments社などが、このタイプの製品を製造している。

AC-DCコンバータの問題点としては、突入電流が挙げられる。突入電流とは、入力スイッチを閉じた瞬間に、入力コンデンサを充電するために必要となる大量の電流のことだ。この電流は整流器のダイオードにストレスを与え、コンデンサが早く故障する原因ともなる。この問題の解決方法の1つとして、入力と直列にNTC(negative temperature coefficient)デバイス(サーミスタ)を配置する方法がある*4)。NTCデバイスは、低温時に大きな抵抗値を持つ。入力電流がコンデンサに流れ込み、NTCデバイスが加熱されると、抵抗値は小さくなる。ただし、NTCデバイスには周囲温度の影響を受けやすいという欠点もある。

2つ目の問題点は、入力コンデンサが大きなスパイク電流を発生させることだ。このスパイク電流は、欧州で販売されている電源に義務付けられているPFC回路を使用すれば小さくすることができる。電解コンデンサにはヒューズを付けることを忘れてはならない。生産直前になってUL(Underwriters Laboratories)の発火試験に落ちるのは、FCCとCEのEMI/RFI(電磁干渉/無線周波数干渉)試験に落ちることと同様に避けたい事態だ。

スイッチングICを使ったAC-DCコンバータのもう1つの一般的な問題に、スタートアップ回路の静止電流がある。この種の製品では、発振や調整が始まるまでに5V〜10Vの電圧を印加する必要がある。このような電圧をチップに供給する際には、大きな抵抗を使わなければならないことが多いだろう。この抵抗を、例えば170V以上のDCバスから5V〜10VのICにかけて配置した場合、かなりの電力損失が発生する。こうしたケースでは、例えば耐圧が500V以上の米Supertex社製ディプレッションモードFETを使うという対処も考えられるが、低コストであることが要求されるケースでは無理だろう。一部のベンダーは、この問題を解決するための新しいアーキテクチャを開発している。その1つであるPower Integrations社でマーケティング部門バイスプレジデントを務めるDoug Bailey氏は以下のように語る。

「パワートランジスタを組み込んだソリューションでは、高耐圧MOS FETを分圧器として使用し、低電圧で小さな電流を取り出す方法を用いる。われわれは自社のすべてのスイッチングICにこの方法を取り入れているが、非常にうまくいっている」。

デジタル電源

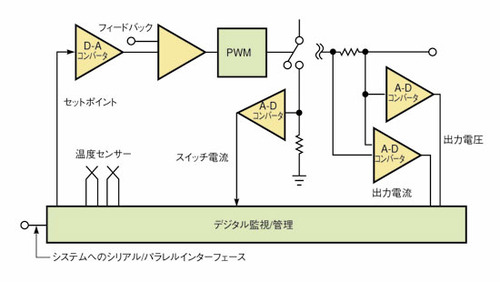

デジタル電源でも、多くの場合、従来のアナログPWMループが使われている。しかし、一般的なシャットダウン機能にとどまらない、かなりの範囲でデジタル方式を用いた監視/管理が行われる(図6)。

デジタル電源の祖先ともいえるものはバッテリチャージャICだ。鉛酸電池などの古いタイプの充電池向けのもので、用途ごとに異なる充電電圧に対応して、セル当たり2.3V〜2.36Vを供給するように設定された電圧レギュレータICがよく使用されていた。こうした単純な電池に向けたICでさえ、充電電圧を調整するための周囲温度感知機能やタイマーリミッタ、セル温度感知機能を備えているものが多かった。ニッケル水素電池やリチウムイオン電池であれば、デジタルによる監視/管理がもっと重要になる。

電池が十分な電圧を供給できない状況にある場合、フルパワー充電を行うべきではない。もしそのような状況になったなら、フルパワー充電ができるレベルに電圧が上がるまで、セルに対して小さな電流を流し、それを監視する必要がある。電池が数時間たっても完全に充電されない場合には、ICによってその充電サイクルを終了させる必要がある。National Semiconductor社のアプリケーションエンジニアMary Kao氏は、「もはやわれわれは、バッテリチャージャICを、何らかのロジックを組み込んだPWM回路としては見ていない。アナログPWM回路を備えたマイクロコントローラだと考えている」と説明する。

バッテリチャージャICが使われるようになると、ほかの多くのアプリケーションでも、アナログPWMループのデジタル制御が求められるようになった。例えば、米Xilinx社のFPGAでは、厳密な電源シーケンス/制御が求められる。また、米Cradle Technologies社のマルチコアDSP(130nmのCMOSプロセスを採用)ではDDR SDRAMが使用されるため、I/O用の3.3V、コア用の1.2V、DDR-SDRAM I/Oの2.5V以外にも、何種類もの電圧が必要となり、電源システムの設計が極めて困難であった。

よりなじみ深い例としては、パソコンが挙げられる。パソコン愛好家のほとんどは、プロセッサとメモリーへの供給電圧がデジタル制御されていることを知っている。また、ハンドヘルドデバイスの電池寿命を伸ばすには、複雑な制御用件が必要となる。

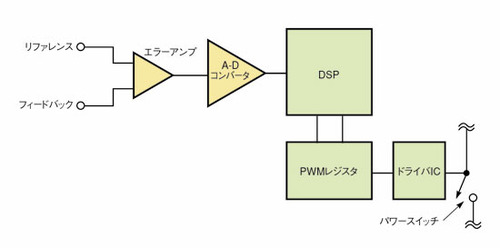

多くのデジタル電源では、ループを安定させるための演算処理に、従来のアナログPWMループではなくDSPが使われている(図7)。この方法であればループ補償回路を柔軟に設計できるが、実はこの柔軟性が高くつくことがある。Elandesigns社のDave Mathis氏は、「補償回路を変更するのなら、その変更の土台となるものを明確にしなくてはならない。捕捉回数と誤差条件を考えれば、厄介になることは目に見えている」と語る。

一方で、米Primarion社は、同社が発表した記事の中で「将来はすべての電源がデジタルになる。デジタル電源を受け入れようとしないアナログエンジニアは、自らの砦を守る以上のことはできないだろう」としている*5)。同社はループ制御にDSPを使用しておらず、消費電力がはるかに少ないステートマシンを採用している。それでも制御はアナログPWMループではなくデジタルループで行われている。

Texas Instruments社デジタル電源部門マネジャのSteven Bakota氏は次のように指摘する。

「デジタル電源は特に新しいものではない。われわれは、標準的なDSPと組み合わせて使用するライブラリの形でデジタル電源を10年前から販売している。そのころと違う点は、『Fusion Digital Power』の製品ラインアップと、実装を容易にするソフトウエア開発環境があることだ」。

デジタル電源システムの制御ループを形成するには、6万個ものトランジスタで構成されるDSPが必要となる。それに対し、アナログ方式であればわずか100個のトランジスタで済むことを認識しておくべきだ。デジタル電源の支持者の中には、「静止時の消費電流が約7mAだ」と自慢するものもいる。確かに、AC電源のコンセントからの電力で動作するブレードサーバーならこの数字でよいだろうが、電池で動作するポータブル製品には受け入れがたいほど大きな電力損失だ。アナログ電源であれば1mA未満で動作する。

設計者はシステムの瞬時電力損失も評価しておく必要がある。DSPを再度初期化してユーザーコードを実行する必要がある場合、一部のアプリケーションには不適切な電力が供給されてしまう可能性があるからだ。

最後の注意点になるが、デジタル電源を利用する場合には、かなり複雑なソフトウエアの開発に労力をかけなければならないことを覚悟しておく必要がある。

脚注

※4…P Seshanna, "Time-delay relay reduces inrush current," EDN, March 7, 2002, p.130.

※5…"Digital power management: Changing the value ecosystem," Aug 1, 2006, Power Management Design Line, www.powermanagementdesignline.com.

Copyright © ITmedia, Inc. All Rights Reserved.

図6 デジタル電源の監視/管理回路 リニアレギュレータの問題点としては、発熱、コンデンサの短絡、ICに逆電流が流れたときの部品の損傷などが挙げられる。

図6 デジタル電源の監視/管理回路 リニアレギュレータの問題点としては、発熱、コンデンサの短絡、ICに逆電流が流れたときの部品の損傷などが挙げられる。 図7 DSPを利用したデジタル電源 デジタル電源では、アナログ制御ループの代わりにDSP(またはデジタルステートマシン)が使用されるケースも多い。

図7 DSPを利用したデジタル電源 デジタル電源では、アナログ制御ループの代わりにDSP(またはデジタルステートマシン)が使用されるケースも多い。