高速化が進むSPICEシミュレータ(1/3 ページ)

アナログ回路のシミュレーションにおいては、現在でもSPICEが主役を務めている。しかしながら、ICに集積される回路の規模が膨大なレベルになるに連れ、従来のSPICEシミュレータでは、現実的な時間内に結果を得ることが難しくなった。この問題に対して、SPICEツールベンダーは、どのように取り組んでいるのだろうか。

速度 vs. 精度

アナログ/ミックスドシグナル/RF分野のIC設計者が、シミュレーションツールに求めることとは何か。それは、速度、精度、使いやすさの3つに集約することができるだろう。アナログ回路のシミュレーションでは、現在でもSPICEシミュレータが最も主要な選択肢である。EDAベンダーらは、シミュレーションツールをマルチコアプロセッサやマルチCPUシステムに対応させるなど、最新の技術を利用して自社ツールの速度と精度の向上を図っている。また、シミュレーションを高速化するために、その中核となるSPICEのアルゴリズムを変更している企業もあれば、トップダウン設計に着目する企業もある。

昨今では、あらゆる製品にRF/ワイヤレス通信機能が追加されるようになってきた。そのことも理由となって、SPICEは、設計者にとって必要なシミュレーションとして存在し続けている。また、RF/ワイヤレス機能を提供しない製品も、IC製造プロセスの微細化、デジタル回路の高速化、高速シリアルI/Oポートの普及に伴い、RF回路と同様の性質を持ち始めている。

SPICEについては、高速化を図ることが1つの大きな課題である。これを、精度を落とすことなく実現することがEDAベンダーにとっての取り組みの中心となっている。本稿では、代表的なSPICEツールベンダーの取り組み状況を紹介していく。

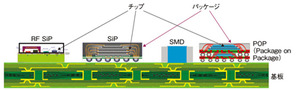

また、用途を問わず高速化/高機能化が求められ、それをより小さな面積で実現しようとすることから、チップと基板を切り離して設計することが難しくなってきた。その結果、チップ、パッケージ、基板をまたがる協調設計/シミュレーションが必須になろうとしている。本稿では、そうしたシミュレーションツールについても、別掲記事で紹介する。

■Cadence社

米Cadence Design Systems社は2008年12月、精度を落とさずに高速化を実現するものとして、SPICEシミュレータ「Cadence Virtuoso APS(Accelerated Parallel Simulator)」を発表した。同製品は、シミュレーション/検証ツール「Cadence Virtuoso MMSIM(Multimode Simulation) 7.1」に組み込まれる。Cadence社のシニアアーキテクトであるJohn Pierce氏は、「この新シミュレータは、従来であれば、数日から数週間を要したミックスドシグナルシミュレーションの実行時間を数時間に短縮する」と語っている。

Cadence社のシニア製品マネジャを務めるNebabie Kebebew氏によると、Virtuoso APSは、シングルスレッド性能とスケーラブルなマルチスレッド性能を大幅に向上させつつ、回路シミュレータ「Cadence Virtuoso Spectre」と同等の精度を維持しているという。同氏は、「20社以上の顧客が、PLL(Phase Locked Loop)、D-Aコンバータ、A-Dコンバータ、メモリー、電源管理回路、高速I/O回路を含む200以上もの設計で、同シミュレータのベータ版を試用した」と述べている。ある顧客の例では、8コアシステム上で実施されるシミュレーションにより、PLL回路(65nmプロセス品)において従来の60倍もの速度を得たという。また別の顧客の例では、DC-DCコンバータのポストレイアウトシミュレーション時間が20時間から16〜20分へと短縮されたという。

■Mentor社

米Mentor Graphics社も、SPICEシミュレーションの高速化に取り組んでいる。同社は2008年10月、トランジスタレベルシミュレーションに対応するアナログシミュレータ「Eldo」および「Eldo RF」の新バージョンをリリースした。これらの製品では、精度を落とすことなく、シミュレーション速度を向上させている。また、行列計算手法が改良されており、安価なマルチCPUシステムの利用を可能にするスケーラブルなマルチスレッド技術も採用している。Mentor社のディープサブミクロン事業開発マネジャを務めるTony Liao氏によると、「マルチスレッド対応のEldoでは、回路内のアクティブ素子の数や寄生要素によってばらつきはあるものの、シングルコア対応の場合よりも3〜10倍以上も高速にシミュレーションが行える」という。

また、同氏は、「より高速なシミュレーションを望む顧客には、精度は幾分劣るが、高速SPICEシミュレータ『ADiT』が適している」と述べている。ADiTとEldoは双方向のインターフェースを備えており、1つの回路に対して両方の製品でシミュレーションを実行することができる。そのため、高い精度を要する部分はEldoでシミュレーションし、そのほかの部分はADiTを使うといったことが行える。

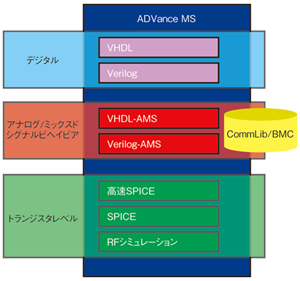

Liao氏によると、両シミュレータは、Mentor社のデジタル回路シミュレータ「ModelSim」との連携が可能であり、協調検証をサポートするという。また、同社の「ICAnalyst」とも連携が可能となっており、設計検証にも対応できる。さらに両シミュレータは、同社のミックスドシグナル検証環境「ADVance MS」内で連携して動作することが可能である(図1)。

なぜ、協調設計ツールが必要なのか?

米Agilent Technologies社の電磁界シミュレータ「Agilent EEsof EDA」部門の製品マーケティンググループに所属するHow-Siang Yap氏は、協調シミュレーション手法について以下のように説明している。

「まず、米The MathWorks社の『MATLAB』や当社の『Ptolomy』のような数値解析ツールと、C++、SystemC、標準的なHDL(ハードウエア記述言語)への対応が必要になる。また、Sパラメータを扱うことができ、調波平衡(Harmonic Balance)法を実装した周波数領域のACシミュレーションも扱えなければならない。さらに、時間領域については、SPICEツールが必要である。設計を行う際、ハードウエアを確定する前に、近接度や遷移の影響のトラブルシューティングを行うために、モーメント法や有限要素解析の利用が可能な電磁界領域のツールを使用するべきだ」。

「ADS(Advanced Design System)」を含むEEsofのツールは、米HP社のRF/マイクロ波計測器グループから派生したものである。2000年にリリースされたADS 1.0は、DSPを含む高速デジタル回路やRF回路のシミュレーションを可能にした。同ツールは、当初はWLAN(Wireless Local Area Network)設計に多く利用されていた。その後、民生機器メーカーが、少ないコストで多くの機能を提供しようと、デジタル、アナログ、RF機能を小さな領域に詰め込むようになるに連れ、チップ、パッケージ、基板の協調設計やシミュレーションの必要性が高まった(図A)。ADSはこうした要求に応えるものとして、改良を加えられている。Yap氏は、「協調設計の工程は、性能とコストの改善に向けてシステムのパーティショニングを最適化するフロントエンドと、ボールパターンの計画、配線、I/Oの最適化などの要素を扱うバックエンドの2つの側面に分けられる」と述べている。

Yap氏は、「最近の進展としては、非線形Xパラメータのサポートが挙げられる」と語る。Agilent社は2008年12月に、「ADSによるシミュレーション、または当社のテスト/計測機器からXパラメータの生成が可能となり、通信機器の開発期間の短縮が図れる」と発表した。Xパラメータにより、設計者はシミュレーション内で使用するモデルを得ることができる。Xパラメータがなければ、数カ月もの特性評価と大量のグラフ作成が必要となり、得られたグラフの解析も困難になる可能性がある。

将来の展望として、Yap氏は「回路からアンテナまでのすべてをシミュレーションするために、設計フローに電磁界シミュレーションを統合しようという試みが引き続き行われるだろう。さらに多くの製品がワイヤレス対応となり、小型の製品では、アンテナが基板上に存在することも多い。ハードウエアを確定する前に、潜在的な問題を検出する能力が必須となる」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング