高速化が進むSPICEシミュレータ(2/3 ページ)

■Synopsys社

米Synopsys社も、SPICEシミュレーションの高速化に取り組んでいる。「HSPICE」の新版を2008年3月にリリースした際には、同シミュレータのコアエンジン技術の改良と、新しいマルチスレッド機能について発表した。Synopsys社でミックスドシグナルシミュレーション製品のマーケティングディレクタを務めるGeoffrey Ying氏によると、「当社は、自社ツールのすべてを、マルチコア対応にするよう改変中であり、HSPICEがその第1弾となる」という。「HSPICEのマルチスレッド版により、ポストレイアウトシミュレーションの速度がシングルコア版の最大3倍となり、4コアプロセッサを利用すれば、最大で6倍の速度が得られる」と同氏は述べる。マルチコア対応版では、抵抗性/容量性の寄生効果が非常に大きいポストレイアウトシミュレーションにも対処可能となっている。

Synopsys社は、台湾TSMC(Taiwan Semiconductor Manufacturing Company)社と共同で、TMI(TSMC Modeling Interface)技術を開発した。同技術は、HSPICEのほか、Synopsys社のシミュレータ「HSIM」、「NanoSim」にカスタムデバイスモデルを統合するためのプロトコルにより構成されている。TSMC社の40nm以下のプロセス技術に対する革新的で効率的なデバイスモデリング手法との位置づけとなる。Ying氏は「TMI技術は、シミュレーション時間を平均で1/5に短縮し、メモリー使用率の低減ももたらす。また、シリコンにおける機械的応力の影響について考慮できる。さらに、ほかの素子との近接度によって素子の特性が変わるレイアウト依存性についても検討が行える」と述べている。

■Magma社

米Magma Design Automation社は、マルチコアやマルチスレッドではなく、マルチCPUシステムをターゲットとしている。同社カスタム設計ビジネス部門のビジネス開発担当シニアディレクタを務めるKT Moore氏によると、同社の「FineSim Spice」では、「当社のNPT(Native Parallel Technology)アルゴリズムを利用して、演算負荷を複数のコンピュータに分散させることで、精度を維持しつつ速度を向上させている」という。「この手法により、100台ものコンピュータを利用するのではなく、8台ほどの実用的な台数で、膨大な数の素子のシミュレーションを行うことが可能になる」と同氏は語る。

マルチスレッド/マルチコアやマルチCPUシステム向けの実装により、SPICEシミュレーションの性能は向上した。しかし、高速化の要求は絶えることがない。Moore氏は、「設計工程のフェーズごとに、精度に対する要求は異なる。初期の段階では機能に目が向いている。設計内容が固まり始め、実際の動作特性に着目し出すと、高い精度が欲しくなる。大規模な設計では、莫大な数のトランジスタを扱うことになる。複数のCPUで動作する当社SPICEエンジンは、サインオフ用のシミュレーションツールとして最適な選択肢だ」と述べる。

■Berkeley社

SPICEの分野では、比較的新しい企業が、古くから存在するEDA企業らとの競争に参入してきている。その戦術の1つは、純粋なSPICEと高速SPICEとの境界をあいまいにすることだ。例えば、米Berkeley Design Automation社のCOO(最高執行責任者)であるPaul Estrada氏は、「高速SPICEツールでは、高速化を実現するために精度を落とす傾向にある」と述べる。それにもかかわらず、メーカーは、そうした高速SPICEツールを“SPICE精度(SPICE-accurate)”とのうたい文句で販売する場合が多い。それに対し、Estrada氏は「当社の『Analog FastSPICE』は、本来のSPICE精度を維持しつつ、高速SPICEの性能を提供する」と主張する。「このツールでは、近似処理は使わない」(同氏)という。同ツールは、回路全体にわたる本来の行列を用い、デバイスの特性を表す本来の式を実行しつつ、ほかのSPICEエンジンと同等か、それらよりも優れた波形を生成するという。

Analog FastSPICEは、シングルコアでの利用を前提としており、それでも高い性能が得られるようになっているという。そのような性能が実現できる背景について、Estrada氏は、「既存のSPICEエンジンのコードを見るとわかるのだが、いずれも、すべてが互いに入り組んだものとなってしまっている。そのため、ある部分を改善しようとすると、必ずほかの部分を劣化させてしまう」と述べる。Analog FastSPICEはモジュールアーキテクチャを採用しており、ほかのモジュールに影響を与えることなく、個々のモジュールを最適化することができる。同社は将来に向けて、マルチスレッド版でも優れた効果が得られることを確認しているが、まだ製品としてはリリースしていない。

システムレベルでの電磁界解析

シミュレーションを徹底的に実施して検証を行ったとしても、実際のシリコンチップが現実の世界に持ち出されたときに、正しく動作するという保証はない。ICの性能は、パッケージ、ICを搭載するプリント配線板(以下、基板)、基板を取り巻く電磁界の影響を強く受けるからだ。

米Ansoft社のビジネス開発担当ディレクタを務めるLarry Williams氏は、ある半導体メーカーの例を語ってくれた。そのメーカーのICは、評価ボード上ではうまく動作した。その評価ボードは、配線トレースの間隔がきちんと空けられ、多くの電源/グラウンドプレーンによって信号線が隔離されていた。しかし、顧客が、トレースの間隔が狭く、はるかにカップリングが生じやすい小型民生機器に搭載すると、そのICは異常な動作を示した。ICの無線機能において、帯域外に許容できないほどのスプリアス応答を示したのである。Williams氏は、「チップ、パッケージ、基板の完全なシステムレベルのシミュレーションを行うことにより、その問題の解決策を示した」と語る。Ansoft社は、問題となったIC向けのSPICEレベルモデルを用意し、3Dでの抽出を行ってICのBGAパッケージと基板のモデルを作成した。「当社ツールの環境にそれらを組み込むことで、問題のスプリアスを再現することができたのだ」と同氏は述べる。

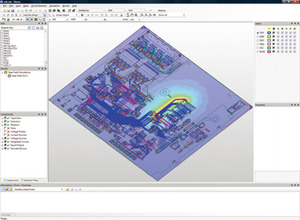

Ansoft社の製品としては、高周波/高速部品の3D電磁界シミュレーションが行える「HFSS」がある。また、「SIwave」は、デバイスのレイアウトデータから周波数に依存する信号線/回路のモデルの抽出を可能とし、シグナルインテグリティへの対応と電力分配の問題を特定するためのツールである(画面A)。「われわれが解決しようとする問題は非常に大きなものである。シグナルインテグリティへの対処は必須だ」とWilliams氏は述べる。「高い信頼性と性能を保証するために、多くの企業がシグナルインテグリティを扱う部門を設置している。最新の携帯型電子機器は、ユーザーの使い勝手を高めるために、数種類の無線通信機能と多くのデジタルコンテンツ対応機能を搭載している。それらは消費電力を抑えるために低い電圧で動作するので、デジタル信号であってもカップリングの影響を受けやすい。われわれは、基板モデルを読み込み、それをICパッケージのモデル抽出結果と組み合わせることで、システムレベルのシミュレーションを可能にする」と同氏は述べた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング