SSDの真の可能性:HDDとの比較と最新技術動向で探る(2/3 ページ)

フラッシュメモリーの特徴

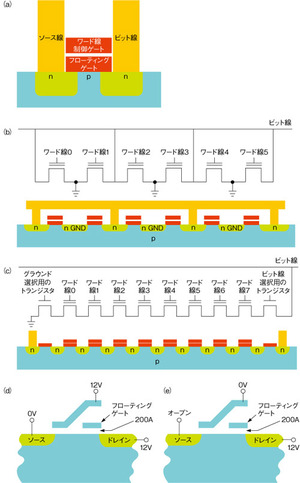

今日のフラッシュメモリーの多くは、フローティングゲートを利用したセル構造を持つ(図1(a))。またフラッシュメモリーには、高速なランダム読み出しアクセスが可能なNOR型(図1(b))と、低速だがビット当たりの単価が安いNAND型(図1(c))がある。両者の主な相違点は、セル間を相互接続する構造にある。

フラッシュメモリーに保存された値を変更する方法は次のようになる。まず0にプログラミングするには、通常よりも高い電圧を印加して、フローティングゲートに電荷を注入する(図1(d))。データの消去(1にする)は、図1(e)のようにして、電荷を除去することで行う。初期のフラッシュメモリーでは、使用する高電圧をチップ外で生成して印加する必要があった。しかし、今日では多くのデバイスが高電圧を生成するためのチャージポンプを搭載している。理論的には、EEPROM(Electrically Erasable Programmable Read Only Memory)、FRAM(Ferroelectric Random Access Memory)、MRAM(Magnetic RAM)、SRAM(Static RAM)と同様に、1から0へのプログラミングと0から1への消去の両方において、ビット単位で値を変更することができるはずである。ただし、それに必要な信号配線や絶縁用の回路などは、チップ上のかなりの面積を占有してしまう。そのため、ストレージ用のICとしてはコストがかかりすぎてしまうこととなる。

一方、最新のNAND型フラッシュメモリーでは、約512Kバイトのブロック単位でデータを消去することができる。ビット単位のプログラミングも可能だが、効率の観点から、SSDとその中のNAND型フラッシュメモリーに対しては、4Kバイト程度の固まりでデータを書き込むほうが望ましい。この値は、フラッシュメモリーチップ上のRAMバッファの容量に依存し、コストと性能のバランスを考慮して決定される。ある一定の単位での変更が必要な点が、フラッシュメモリーベースのSSDと、ほかの不揮発性メモリーストレージやHDDとの相違点だ。

プログラミングサイクルと消去サイクルが繰り返されると、フラッシュメモリーにおけるトランジスタ基板とフローティングゲートの間の薄い酸化膜を電子が何度も通過する。これにより酸化膜がダメージを受け、チップの劣化という事象が起きる。劣化の初期段階では、一部の電子が酸化物の格子にトラップされ、ほかの電子の流れを妨げて、プログラミングや消去の処理が遅くなる。さらに劣化が進むと、最後には酸化膜が破損し、基本的なトランジスタ構造が崩れてしまう。多くの場合、この故障したトランジスタを含む消去ブロック全体が書き込み不能になる。

■SLCとMLC

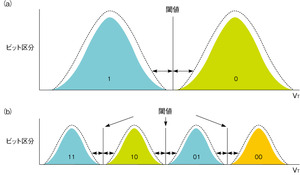

データ保持構造に着目すると、現在、流通しているフラッシュメモリーには、SLC(Single Level Cell)、MLC(Multi Level Cell)の2種類がある。SLC方式では、トランジスタアレイの出力に接続する電圧検知回路は、比較的単純なものでかまわない。1つの閾(しきい)値電圧のみを検知すればよく、トランジスタの1と0の出力電圧は、この閾値からかなり離れた値となる(図2(a))。一方、2ビット/セルのMLC方式では、読み出しの際に検知すべき閾値電圧が3つあり、4レベルの判別が必要になる(図2(b))。このため、フローティングゲートに電荷を注入するプログラミング処理も高い精度を要する。さらに電源電圧の変動や温度の変化、消去サイクル数による劣化の影響も考慮しなければならない。そのため、SLCと比較してMLCはプログラミングが難しく、信頼性が低い。米Spansion社は、同社のMLC技術である「MirrorBit」により、電荷注入の高精度化の必要性が軽減できると主張している。だが、概念的には同じことが当てはまると言える。

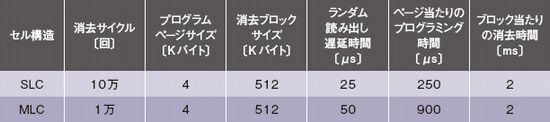

SLCとMLCの構造の違いは、性能の違いとなって現れる。一般的にMLCはSLCよりも読み書きがかなり遅く、対応可能な消去サイクル数は平均でSLCよりも1桁ほど少ない。表1は代表的なSLCのNAND型フラッシュメモリーとMLC(2ビット/セル)のNAND型フラッシュメモリーの仕様を比較したものである。SLCと比べて、 MLCは消去サイクル数が少なく、プログラミング時間が長い。構造の差からこのような性能の差が出るのは、当然のことだと言えよう。MLCのメリットは、ストレージデバイスのビット当たりのコストを低く抑えられることである。だが、一方で性能が低下するというデメリットがある。このトレードオフを念頭において機器に用いるべきだ。

現在、米Intel社と米Micron Technology 社は、3ビット/セルのフラッシュメモリーを提供している。また、米SanDisk社は、4ビット/セルのフラッシュメモリーである「X4」の製造を開始した*2)。これらのMLCフラッシュメモリーにおいて、隣り合うデコードビットの閾値電圧は、電子100個分以下の電荷の差に相当するという。このことは、半導体プロセス技術者、製品技術者にとって、かなり難易度の高い課題となる。おそらく、性能とデータの信頼性を犠牲にすることになるため、信頼性の高いストレージを必要とする用途には適さないかもしれない。ただし、ほんの少し前までは、2ビット/セルのMLCフラッシュメモリーに関しても同じことが言われていた。従って、この問題については、今後、新たな技術によって改善されるだろう。

脚注

※2…"Engineering Windows 7," Microsoft Corp, 2009. http://blogs.msdn.com/e7/archive/2009/05/05/support-and-q-a-for-solid-state-drives-and.aspx

Copyright © ITmedia, Inc. All Rights Reserved.