モバイルテレビ向けLNAの設計:バイパス機能で強電界入力に備える(3/4 ページ)

設計と製作

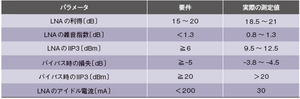

表3に、モバイルテレビの受信機用LNAについて、テレビメーカーの設計者が要求するRF仕様の一例を示す。例にとったのは、47MHz〜870MHzで使用できるアナログ/デジタルのデュアルモードLNAである。顧客に受け入れられるには、当然、性能要件のほかに、部品点数が少ないことや実装コストが低いことも重要である。以下では、前節で挙げた3つのうち、2番目のバイパスモードを設ける方式について、部品点数を抑え、なおかつ低コスト化を図りつつ、このような厳しい要求を満足させる方法について詳しく説明していくことにする。

■部品の選択

筆者らは、表3の仕様を踏まえて、実際にLNA回路を設計しプロトタイプの製作を行うことにした。まず、増幅素子とスイッチング素子の両方を集積した製品として、アバゴ・テクノロジーの製品群から既存のMMIC(マイクロ波モノリシック集積回路)を候補として検討した。具体的には、「MGA-72543」あるいは「MGA-785T6」であれば、FET(電解効果トランジスタ)ベースで集積度が高く、コストや実装面積、消費電流の面で有利だと考えたのである。しかし、各製品の仕様を確認したところ、これらのMMICでは、広帯域特性と線形性の要件を満たせないことがわかった。同様に、LNAと1対のRFスイッチを集積した他社製品も存在するが、筆者らの知る範囲では、表3に示したような厳しい要求を満足しているものは存在しない。また、このような構成のICで、表3のような厳しい仕様を満たすものを開発するのは非常に困難なことである。

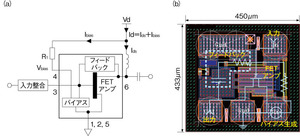

最終的に、広帯域で線形性の高いLNAのMMIC「MGA-68563」を、PINダイオードから成る外部RFスイッチと組み合わせて構成することに決定した。この製品は、ゲート幅が800μmの1段GaAs(ガリウムひ素) pHEMT(Pseudomorphic High Electron Mobility Transistor)増幅器である(図3)。プロセス変動を補償し、閾(しきい)値電圧の変動の影響を最小にするために、素子のゲートをカレントミラーに接続してある。これにより、減衰特性を持つ負帰還を利用して回路を安定化させることができ、0.1GHz〜1GHzの周波数応答が偏差3dBで平坦化される*8)。この製品であれば、0.1GHz〜4.0GHzにおいて安定係数値が1以上で(k≧1)、無条件安定であることが確認できた。

このMMICは、本来、単一周波数用途向けに設計されている。そのため、製品仕様書では、1つの直列インダクタで構成した単純な入力マッチング回路を使うことを推奨している。上述した帰還回路によって、1GHz未満の出力リターンロス(ORL)が十分に小さくなる(≦−10dB)ので、出力整合は必要としない。しかし、一般的なLC回路網を使って47MHz〜870MHzの周波数範囲で入力を整合させることは困難である。RFトランスを用いれば必要帯域幅の全体にわたって入力を整合させることができるが、コストと寸法/高さを理由に使用を断念した。

■設計の詳細

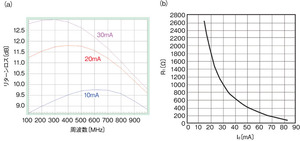

上述した状況に対応するために、筆者らは、入力リターンロス(IRL)を最適化する方法として、FETのドレイン電流(Ids)を公称値である10mAより増やすという手段を採用した。Idsを20mAとすることで、必要なIRL(≧10dB)は満たされるが、PINダイオードスイッチ回路を追加するので、IRLにはより多くのマージンが必要となる。そのため、最終的にはIdsの値として30mAを選択した(図4)。図3(a)に示したように、同MMICでは、4番端子に外部抵抗R1を接続し、内部バイアス回路に流れる電流を制御する。つまり、電源電圧(この例では3.0V)を固定したままR1を変更すれば、Idsを変えることができる。Idsを10mAから30mAと3倍にすることで、線形性の向上というもう1つの効果も期待できる。

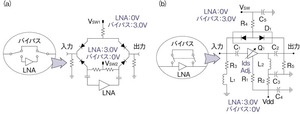

最初の設計段階では、スイッチによるバイパス機能付きLNAを実現するために、4つのPINダイオードを使う必要があると考えていた(図5(a))。PINダイオードを使用してDPDT(双極双投)スイッチを実現する極めて標準的な構成であり、送信中にLNAをバイパスしなければならないケースでも一般的に用いられている。この回路は、図における下側のPINダイオード対をバイアスせずに上側のPINダイオード対をオンにしたり、逆に上側をバイアスせずに下側をオンにしたりすることでスイッチングを行う。通常の動作では、下側のPINダイオード対だけがオンになり、LNAによってRF信号が増幅される。一方、利得を低下させたいときは、上側のPINダイオード対だけをオンにして、LNAの信号をバイパスする(バイパスモード)。抵抗は、PINダイオードの順電流を制御し、RF信号と制御ポート(VSW1とVSW2)の分離を図るために必要になる。

この回路は、性能面では想定した特性を満たす。しかし、図5(a)は機能概要のみを簡略化して示したものであり、実際には部品点数が多くなるため、このままでは小型化の要求には応えられない。

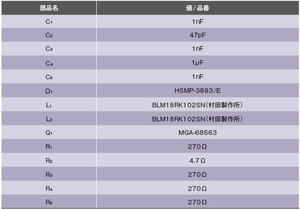

こうした問題点を解決するために、PINダイオード数を半減する別の回路構成を考案した。図5(b)に示した設計では、DPST(双極単投)構成のPINダイオードスイッチによって、バイパス経路だけが入出力ポートに接続されたり遮断されたりする。各部品の値や品番は表4に示したとおりである。

この方法では、LNAの経路にはスイッチング素子が存在しない。バイパスモードは、バイアスされていないFETによるアイソレーションを利用することで実現する。バイアスされていない状態は、LNAの電源(Vdd)を遮断することで作り出す。このとき、実際にはFETのゲート、ドレインは完全なオープンの状態ではなく、それぞれのインピーダンスが接続された状態となる。そのため、バイパス経路にはリターンロスが生じることになる。通常動作の際には、PINダイオードの電源は0Vとし(VSW=0V)、LNAの電源は3.0Vに戻す。しかし、バイアスのかかっていないPINダイオードにも、ある程度の寄生容量が存在するため、高い周波数の信号が通過する。すなわち、バイパス経路を入出力ポートから完全に切り離すことができず、LNAの利得の低下に加え、リターンロスが生じることになるので注意が必要だ。

図5(b)のL1とR3は、フェライトビーズインダクタである。これらにより、PINダイオードとMMICのバイアス回路網において、周波数範囲全体で高インピーダンス特性を得ることができる。L1のチョーク作用がない場合、入力信号の一部は、R3に並列に存在する寄生容量によってグラウンドに並列に落とされる*9)。後ほど結果を示すが、L1を使用しないプロトタイプを作成して評価を行ったところ、この信号損失がLNAの雑音指数を劣化させることがわかった。

C3、C4、C5の値は、RF信号をDC電源から分離し、最低動作周波数で低リアクタンス(Xc≦5Ω)になるよう決定する。C1とC2は、MMICの入出力をAC結合する。C2としては、高い周波数でMMICの利得ロールオフを補償する高域通過特性を持つように、小さな値を選択する。R1とR2は、MMICに供給する電流量を制御し、Vddが3.0Vのときにバイアス電流が30mAになるよう決定する。R3、R4、R5は、VSWが3.0VのときにPINダイオードの順バイアス電流を1個当たり2.5mAに制限する。

理論的には、D1として1つのPINダイオードだけを使用することにより、回路をさらに単純化することができる。しかし、デュアルタイプのダイオードは、シングルのダイオードと同じSOT-23/SOT-323パッケージで入手でき、価格差もほとんどないことから、そのようにする大きなメリットはない。さらに、ペアのPINダイオードは、次のような2つの大きな性能上の利点を提供する。それは、直列接続の寄生容量が半分になることと、逆向き/直列に接続したPINダイオードによって生成される偶数次高調波の位相は反転しているため、自動的に相殺されることである*10)。

■プロトタイプの組み立て

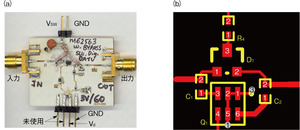

設計した回路のコンセプトを実証するために、プロトタイプを製作した*11)。その際、RF性能を素早く評価するために、以前、バイパス機能を持たない別のLNA用に設計されたプリント基板を用いることとした。この基板は、厚さ10mil(0.254mm)の米Rogers製「RO4350B」を用いており、マイクロストリップライン配線を採用している*12)。PINダイオードとそのバイアス回路を構成する部品は、ほかの部品のリード/パッドに直接はんだ付けすることによって、既存のプリント基板に後付けした(図6(a))。スイッチング素子D1としては、ダイオード「1N5719」(アバゴ・テクノロジー製)を2個を使用した*13)。これらのダイオードは、最終的なレイアウト設計では、SOTパッケージのペアPINダイオード「HSMP-3893/E」(アバゴ・テクノロジー製)に置き換えることにした(図6(b))*14)。

脚注

※8…Avago Technologies product specification, "MGA-68563 Current-Adjustable, Low Noise Amplifier," http://www.avagotech.com

※9…Vishay Intertechnology, Inc. application note AP0010, "Resistors in Microwave Applications"

※10…Avago Technologies application note 1049, "A Low Distortion PIN Diode Switch Using Surface Mount Devices," http://www.avagotech.com

※11…Avago Technologies application note 5011, "MGA-62563 High Performance GaAs MMIC Amplifier," http://www.avagotech.com

※12…Rogers Corporation product specification, "RO4000 Series High Frequency Circuit Materials," http://www.rogers-corp.com

※13…Avago Technologies product specification, "1N5719, 1N5767, 5082-3001, 5082-3039, 5082-3077, 5082-3080/81, 5082-3188, 5082-3379 PIN Diodes for RF Switching and Attenuating," http://www.avagotech.com

※14…Avago Technologies product specification, "HSMP-389x Series Surface Mount RF PIN Switch Diodes," http://www.avagotech.com

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング