コンパレータにヒステリシスを追加:Design Ideas

コンパレータに、ヒステリシスを持たせたいケースがある。一般的に、これを実現するには、コンパレータの出力端子と非反転入力端子を抵抗ネットワークでつなぐ正のフィードバック構成が利用される。しかし、この方法では、ヒステリシスの2つの閾(しきい)値電圧が固定レベルになる(または、固定レベルとすることが前提となる)。加えて、その閾値電圧がコンパレータの出力回路の飽和電圧によって決まり、さらにその精度が負荷条件に依存してしまうという問題がある。

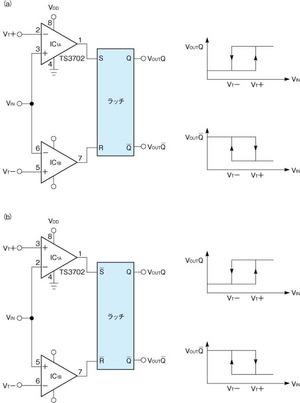

このような問題に対する改善策として、図1の回路を紹介する。この回路では、ヒステリシスの閾値電圧を個別に、簡単に、正確に設定することができる。2個のコンパレータで構成しており、そのうち一方に+側の閾値電圧VT+を入力し、他方に−側の閾値電圧VT−を入力する。そして、各コンパレータの出力がSR(セット−リセット)ラッチを駆動する構成になる。ラッチとしては、入力論理が正(図1(a))または負(図1(b))のどちらのタイプのものでも使用できる。

図1には示していないが、閾値電圧VT+とVT−の生成には、高精度基準電圧と分圧用の抵抗を組み合わせて生成する一般的な手法を用いればよい。あるいは、デジタル的に操作したい場合には、D-Aコンバータを電圧源として使用する方法などが考えられる。いずれの方法も、コンパレータの入力インピーダンスが高いため簡単に実現可能だ。なお、ラッチを使用することにより、20ns〜30ns程度の伝搬遅延が余分に加わることになる。しかし、低速〜中速の用途であればこれは無視できる。

Q出力しか持たないラッチを使用して反転出力を得たい場合には、ラッチに入力するコンパレータ出力を入れ替えればよい。

また、コンパレータの出力がバイポーラ回路型であるか、ラッチの電源電圧より高いレベルの正出力である場合には、出力がオープンコレクタまたはオープンドレインのコンパレータを使用することで対応できる。この場合、クランプダイオードを使用する必要はなく、単に、ラッチの電源とコンパレータ出力の間にプルアップ抵抗を挿入すればよい。

図1では、IC1として、スイスSTMicroelectronics社製のプッシュプル出力段を持つデュアルコンパレータ「TS3702」を使用している。この場合、コンパレータの電源電圧はラッチの電源電圧と同じにしなければならない。

Copyright © ITmedia, Inc. All Rights Reserved.