スイッチドキャパシタ方式のDC-DCコンバータ:Design Ideas

抵抗を介してコンデンサを充電する場合、その電力効率は50%となる。このことから、DC-DCコンバータをスイッチドキャパシタ方式で構成するケースはまれである。しかし、この50%という効率は、初期電圧が加わっていないコンデンサに対して充電する場合にのみ成り立つものだ。言い換えると、予備充電されたコンデンサを用いるのであれば、100%に近い電力効率でエネルギーを伝達することが可能になるということである。

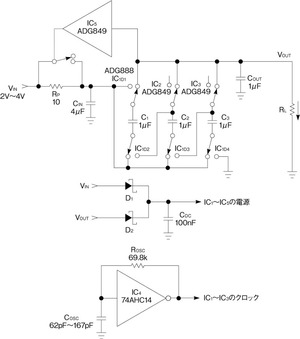

図1に示した回路は、上記のような考えに基づいて、スイッチドキャパシタ方式を利用することで構成したDC-DCコンバータである。この回路では、入力に供給される電圧VINの4/3倍の電圧値を出力として得ることができる。その動作は、以下に示す2つのフェーズに分けられる。

まず1つ目のフェーズでは、各スイッチを操作し(スイッチを図1に示している状態とは逆側に倒す)、同じ容量値の3個のコンデンサC1、C2、C3を直列に接続した状態とする。この状態で入力電圧VINによって3個のコンデンサを充電する。そうすると、各コンデンサは入力電圧VINの1/3の電圧で充電されることになる。

次に、2つ目のフェーズとして、各スイッチを逆側に切り替える(つまりは、図に示した状態になる)。それによって、3個のコンデンサを並列に接続した状態とし、それを入力電圧VINで充電されているコンデンサCINに接続する。その結果、入力電圧VINの4/3倍の出力電圧VOUTが得られる。

この回路は、これら2つのフェーズの動作を繰り返すものとする。以下では、その動作クロックの周波数を変数fで表すこととしよう。

各部品がどのような役割を果たすのか、もう少し詳しく説明する。まずコンデンサCINと同COUTは、それぞれ入力、出力のフィルタリング用のものとして機能する。また抵抗RPは、電源を投入した際の保護用の部品である。これにより、各コンデンサへ流れ込む突入電流の値が制限される。そして、スイッチドキャパシタの動作によって出力電圧VOUTが高くなると、IC5のスイッチが閉じてこの抵抗は短絡される。ショットキーダイオードD1と同D2は、出力電圧VOUTが上昇するまでは、入力電圧VINを使って各ICに電源を供給するように働く。スイッチドキャパシタの動作によって出力電圧VOUTのほうが入力電圧VINよりも高くなると、出力電圧VOUTが各ICの電源として供給される。コンデンサCDCは、この電源経路に対するデカップリングのためのものである。

なお、IC1、IC2、IC3の各スイッチICは、ブレークビフォーメイク(Break Before Make)で動作する。この点が本回路における1つのポイントである。

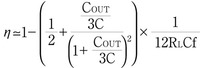

このDC-DCコンバータでは、スイッチIC1のオン抵抗が0.4Ωと小さいことから、損失が少なく、高い電力効率が得られる。理論的な電力効率は、動作クロックのデューティサイクルが50%である場合、次式によって計算することができる。

ここで、変数CはC1、C2、C3の容量値、RLは負荷抵抗の値である。仮に、COUTの値もCであるとすると、3個のコンデンサの充電に伴う電力損失は、放電フェーズの期間における電力損失の約2/3になる。

なお、スイッチドキャパシタ動作以外に、制御動作でも電力損失が生じるので、実際の効率は上に示した式による計算値よりも低くなる。CMOS回路の場合、電力損失は動作周波数に比例して増大するが、動作周波数を適切に選択することにより、回路全体の効率を最適化することができる。動作周波数としては、負荷抵抗RLに反比例する値を選ぶことになる。これにより、効率の特性はRLの値に対してフラットなものとなり、RLの広い範囲に対して90%以上の高い効率が得られる。

具体的には、100kHz〜400kHzのクロック周波数範囲で120Ωの負荷を駆動する場合、94%の効率が得られる。動作周波数を229kHzに設定した場合には、2.2Vの入力に対し、95.9%の効率で2.87Vの出力が得られる。最適なクロック周波数は、負荷が軽くなると、より低い値にシフトする。

Copyright © ITmedia, Inc. All Rights Reserved.