SoC電力解析の有用性:65nm製品への適用例で見る (1/2 ページ)

半導体製造プロセスの微細化が進むに連れ、ICの動作の信頼性を保証するために用いられる、電源グリッドの電力解析の重要性も高まっている。その半面、より複雑な電源構成を持つ昨今のICでは、解析の難易度が上がっていることも事実だ。本稿では、65nmプロセスで製造するSoCの設計について行った解析の手順と、解析結果を紹介する。

SoCでは解析がより複雑に

ICにおいて電源グリッドの電力解析を正確に行うことは、その動作の信頼性を保証するために重要なことである。この検証作業は、65nm以降の微細なプロセスで製造するICでは特に重要になる。チップ上での電源分配に関する問題に起因した再スピンには、コストと時間がかかる上に、ビジネス機会の喪失につながりかねない。

しかし、特にデジタル回路、アナログ回路、ならびにサードパーティ製のIP(Intellectual Property)などから構成される複雑な構造のSoC(System on Chip)の電源グリッドの電力解析は、困難な作業になる可能性がある。これに、複数のコーナー条件におけるばらつきが加わり、さらに静的解析と動的解析の結果に相違があると、電力解析はさらに厄介なものとなる。

本稿で取り上げるのは、65nmプロセスで製造するSoCの例である。このSoCは、異なるベンダーの複数のIPブロックやメモリーを搭載したものであった。グラフィックス処理機能を備えており、動作周波数は200MHz。また、400万個以上のインスタンスと複数のクロックドメインを持つ。ある程度の規模で量産する機器に搭載する製品として開発したものであり、電源分配回路の信頼性を保証することが非常に重要だと位置付けられていた。

この製品の解析では、テープアウト期限の厳守のほか、以下に挙げるような事柄が課題になった。

- 解析用の入力データの準備

- IR(電流、抵抗)ドロップの解析

- 静的/動的な手法によるEM(エレクトロマイグレーション)解析の実施

- 上記の解析で明らかになった問題の特定と修正

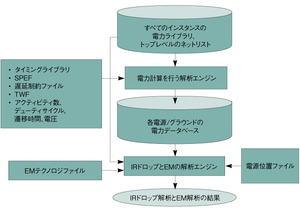

本稿では、主に上記の項目について紹介する。なお、このほかにも、アナログ/ミックスドシグナルIPの取り扱いや、ツール間でのデータのインポート/エクスポートに関する問題を解決する必要もあったが、本稿ではこれらについては触れない。また、このSoCの解析では、図1に示すような標準的な電力解析フローを用いた。

入力ファイルの準備

最初のステップでは、スタンダードセルとマクロの消費電力に関する特性評価を行う。このステップでは、セルまたはマクロの物理的なレイアウトからネットリストと寄生素子のデータを抽出することにより、電力に関する特性評価を行うためのライブラリを生成する。なお、特性評価は、さまざまなレベルの詳細さで実施することができるが、その詳細さの度合いによって実行に必要な時間と精度が変わる。

IPの電力ビュー(Power Views)は、いくつかの方法で入手することができる。たとえば、利用するファウンドリがIPと電力解析ツールを正式にサポートしている場合は、IPの開発者がその電力解析ツール向けに電力ビューを作成済みである可能性が高い。それ以外のケースでは、関連するIPやツールのベンダーが電力ビューを作成してくれるかもしれない。ただし、電力ビューを別途作成してもらう場合には多大な時間を要する可能性がある。

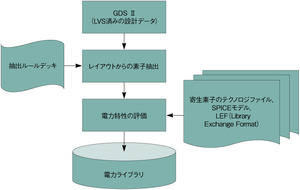

IPブロックを社内で開発した場合など、電力ビューが存在しないケースがある。その場合には、図2のようなカスタムの電力ビュー作成フローを実行して、互換性のあるビューを作成する必要がある。この作業では、LVS(Layout Versus Schematic)に問題がないことを確認済みのレイアウトデータ(GDS IIデータ)から素子抽出を行い、電力特性評価ツールを実行してブロックを解析しなければならないため、非常に複雑なものになるかもしれない。正しいテクノロジファイルの作成は、困難で時間のかかる作業だが、ここでも、テクノロジファイルを提供していないかどうかを関連するベンダーに確認してみるとよいだろう。筆者らの例では、ファウンドリとツールベンダーが、65nmプロセスのすべてのテクノロジファイルを作成済みであった。

電力解析を行うためには、タイミングライブラリ、アクティビティファクタ、電源位置ファイル、物理的/抽出ネットリスト、タイミングウィンドウファイル(TWF)、SDC(Synopsys Delay Constraint)ファイルなどが必要だ。これらはすべて、どこからか入手するか、自分で作成するかしなければならない。

まず、タイミングライブラリには、ゲートの内部電力に関する情報を列挙した電力ルックアップテーブルが含まれる。電力ルックアップテーブルは、入力遷移時間と出力ネット容量の関数として構成される。電力解析ツールは、これらの入力値を用いて、セル内の総消費電力を算出する。

次に、アクティビティファクタは、通常はブロックレベルでグローバルに定義されるもので、設計においてノードの状態がトグルされる頻度を表す。設計したロジック回路にアクティビティファクタを適用し、フリップフロップに明示的にアクティビティファクタを設定することで、より現実的な結果を得ることが可能になる。最も正確な方法は、ゲートレベルのVCD(Value Change Dump)ファイルを使用して、ノードのトグルの様子を正確に把握することだが、そのためにはIRドロップのワーストケースを表すVCDファイルを入手しなければならない。また、VCDファイルを用いた解析は、実行時間が長くなることが多い。

電源位置ファイルは、チップ上の電源とグラウンドの正確なXY座標を示すものである。この情報により、設計者は選択した位置で、バランスの取れた電源分配がなされるのかどうかを確認することができる。通常、チップレベルでは、これらの位置は電源パッドとグラウンドパッド上にある。

物理的ネットリストファイル(DEF)には、SoCの設計におけるセルの配置、配線、接続情報が含まれる。DEFには標準的なフォーマットが存在するものの、一部の配置配線ツールでは、すべての情報を網羅した完全なDEFを作成する際に、複数の問題が発生する可能性がある。最終的には、複数の不完全なDEFから1つの完全なDEFを作成するためのスクリプトを記述し、このスクリプトによって作成された新しいDEFを電力解析ツールで使用する必要があるかもしれない。

抽出ネットリストのSPEF(Standard Parasitic Exchange Format)ファイルとTWFは、設計に対して解析を行う際の一般的なプロセスから得ることができる。抽出ツールが生成するSPEFファイルには、配線における寄生抵抗/容量のデータが含まれる。TWFを生成するのは、STA(静的タイミング解析)ツールである。TWFには、スイッチングウィンドウや遷移時間といったダイナミック電力に大きな影響を与える要素に関する情報が含まれる。

SDCファイルには、クロックドメイン情報、クロック周期、タイミングに関する制約条件が含まれる。同ファイルに、デフォルトのクロック周波数が指定されていない場合には、電力解析ツールのコマンドファイルでそれを明示的に定義することが可能である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング