SoC電力解析の有用性:65nm製品への適用例で見る (2/2 ページ)

解析の実行

ここまでに挙げた各種入力ファイルの準備を終えれば、インスタンスベースの電力計算による解析を開始することができる。電力解析ツールの解析エンジンは、設計の各インスタンスから各セルが消費する電力を計算し、それを内部電力、外部スイッチング電力、リーク電力に分けて報告してくれる。ここで、内部電力とは、セル内部の容量に対する充電/放電で生じる電力と、貫通電流(クローバ電流:Crowbar Current)による電力から成る。これらは、セル内の負荷容量、動作電圧、動作周波数、アクティビティファクタの関数となる。一方、外部スイッチング電力とは、基本的に、セルに接続された配線の寄生容量を充放電するのに必要な電力のことであり、入力に用いるSPEFファイルを用いて算出される。外部スイッチング電力の値には、負荷容量、動作電圧、動作周波数、アクティビティファクタなどの要素が影響を与える。最後に、リーク電力とは、セルの動作とは基本的に無関係に生じる静的な電力のことである。

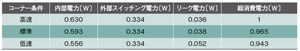

表1に、異なるコーナー条件における電力解析の結果を示す。これは、伝播型のアクティビティファクタを用いて得られた総消費電力の最大値を1Wに正規化して示したものである。高速となるコーナー条件で、より多くの電力が消費されていることがわかる。

次に、解析コマンドファイルのパラメータの値を変化させて得た比較結果を示す。グローバルアクティビティファクタを変化させると、表2に示した結果が得られた。これを見ると、グローバルアクティビティファクタを増加させると、VDD、VSSに対するIRドロップとEM耐性、それぞれの結果が悪くなることがわかる。予測どおりの結果だが、その変化は線形ではない。

グローバルアクティビティファクタを変化させた場合の結果を比較するだけでなく、グローバルアクティビティファクタを指定した場合と、伝播型のアクティビティファクタを指定した場合の違いを比較することもできる。表3に、グローバルなアクティビティファクタを15%に設定した場合の解析結果と、伝播型のアクティビティファクタを適用した場合の解析結果を示す。後者のほうが、IRドロップ、EM耐性、消費電力のいずれも良い値が得られていることがわかる。

静的解析とベクトルなしの動的解析を実行し、それぞれの最も悲観的な場合の解析結果を用いることにより、設計上の問題点を把握しやすくなる。高い温度や高いアクティビティファクタなど、非常に悲観的な動作条件を使用することにより、エラーを強調することが可能である。

解析結果の確認

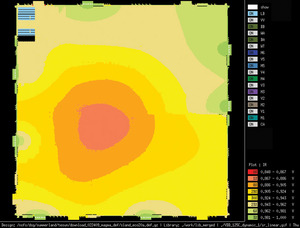

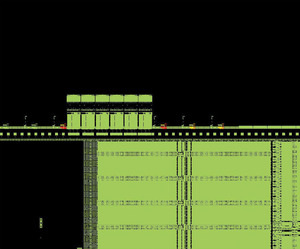

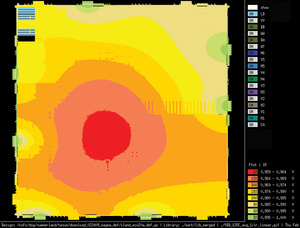

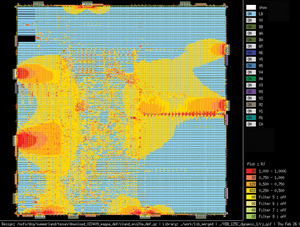

図3、図4はVDDの解析結果であり、チップの左上にある電源グリッドに問題があることが示されている。このような問題は、静的解析を行うだけでは明らかにならない(図5)。図6は、チップの電流密度分布を示したものである。赤い領域は「電流密度が高い」ことを表している。これらの結果を参考にして、物理設計チームはレイアウトを修正することになる。その上で再度解析を行い、設計を検証へと進めればよい。なお、VDDだけでなく、VSSに対しても同様の解析が必要である。

以上に述べたように、さまざまな設計ツールや解析ツールと、ファウンドリやツールベンダーからのサポートを活用することにより、SoCの設計に対する電力解析が効果的に行える。特に、検証によって入力アクティビティに関するデータを得ることができる場合には、静的解析とベクトルなしの動的解析を実行することにより、1種類の解析では特定できないかもしれないような問題を検出することが可能になる。このことは、設計したSoCを量産段階まで移行する上で大変有用である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング