第29回 FPGAの組み込み開発最前線(後編):FPGA Insights

組み込みシステムの開発現場では、消費電力やコストを抑えつつ、性能や機能の向上を実現するための努力が続けられている。その解決手法の1つとして、プロセッサのマルチコア化や専用ハードウエアによるデータの並列処理といった技術を採用する動きが本格化している。本稿では、その一例として、多様なニーズに応えつつ、高性能/低消費電力の両立を可能とする最新のFPGAソリューションについて解説する。

2つの高速化手法

『FPGAと組み込み開発最前線(前編)』でも述べたが、システムの性能を向上させるには、いくつかの手法がある。これまで行われてきたのがプロセッサの動作周波数を高めていく方法である。しかし、この方法だと演算性能の向上とともに、消費電力も増えてしまう。こうした課題を解決する手段として、「FPGAを用いてプロセッサ自体の最適化/カスタム化を行う」、「プロセッサとハードウエア・アクセラレータを併用する」、もしくは「カスタムのマイクロコントローラを開発する」などの方法がある。

ここでは、アルテラのFPGAを用いて、ソフトウエア処理をより高速化するための2つの手法をより詳しく紹介する。その1つが32ビットのソフトコア・プロセッサ「Nios II」への『カスタム命令の追加』である。前述の通り、Nios II には「高速タイプ」、「エコノミータイプ」および「標準タイプ」と3種類のソフトウエアコアが用意されているが、これらには以下に挙げるような共通の特徴がある。

- 最大256命令をユーザー定義することが可能

- 固定または可変サイクルの動作を定義

- SOPC Builderの「Wizard」(操作ガイド)により、容易にユーザー回路の取り込みが可能

- C言語によるマクロとして呼び出す

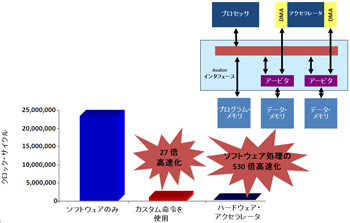

ソフトウエア処理を、より高速化するためのもう1つの手法が『C2H(C-to-Hardware)アクセラレーション・コンパイラ』を用いることである。有料オプションではあるが、ハードウエア・アクセラレーションは、プロセッサとアクセラレータ(専用ハードウエア)を並列に動作させることができる。これにより1クロック当たりの仕事量が増えるため、動作周波数を下げても処理能力を維持または向上することができる(図3)。この結果、消費電力とコストの両方を削減することが可能となる。

C2Hアクセラレーション・コンパイラの特徴は以下の通りである。

- ハードウエア・アクセラレ―タ部は、自動で生成・統合される。

- 直感的なユーザーインタフェースで効率的なCプログラムを加速化。

- Nios II 統合開発環境(IDE)上で操作することができる(右クリックでアクセラレート)。

C2Hアクセラレーション・コンパイラを有効に活用するために設計者は、まずソフトウエア処理においてボトルネックとなっている部分を把握する必要がある。無償で添付されている「GNU/GMON」などを使って、記述されたソフトウエアプログラムを解析すると、処理負荷の大きいプログラムコードが一目でわかるように表示される。そこで表示されたボトルネック部分のプログラムコードを右クリックすれば、その部分を処理するためのハードウエア・アクセラレータが自動的に生成される。これによって、タスクの処理時間を平準化することができる。

上述した高速化手法を採用して、CRCアルゴリズム(64Kバイト)の処理を実行した結果、Nios II にカスタム命令を追加した場合は、ソフトウエアのみで処理した場合に比べて、27倍の高速化を実現することができたという。また、ハードウエア・アクセラレータを併用した場合には、ソフトウエアのみで実行したときに比べ、530倍の処理性能が得られた。

ARM/MIPSコアが実装可能に

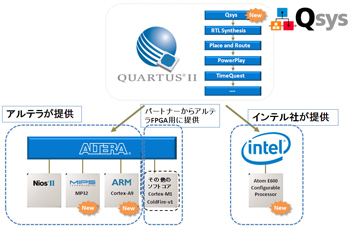

アルテラは、2010年10月、組み込みシステムにおけるプログラマブル・ロジックとプロセッサの融合を加速させるための「エンベデッド・イニシアティブ」を発表した。この中で、開発ソフトウエア「Quartus II 」にシステム・レベル統合ツール「Qsys」が新たに追加された。また、同社のFPGAファミリで対応するプロセッサコアの種類として、Nios II に加えて、ARM社の「Cortex-A9」、MIPS Technologies社の「MP 32」などが新たに追加されることとなった。多様なSoCの設計ニーズに対応できるIPコアのサポートと、これらを活用するための設計環境が整ったことになる(図4)。

複数のプロセッサコアをはじめ、メモリーブロックや特定の信号処理回路、各種インタフェースなどを1個のシリコンチップに集積したSoCでは、これらのIPブロック同士を内部接続するために、オンチップバスが用いられる。内部バスを含むシステム・レベルの設計では、SoCとしての性能を最大化するための技術知識やノウハウが必要となる。処理能力の高いプロセッサコアを実装しても、例えばプロセッサとメモリーと接続するバスのデータ伝送能力が期待値を下回る場合、いわゆる「バスネック」という現象が生じて、プロセッサの性能を十分に生かすことができなくなることもある。FPGAを用いてSoCを設計する場合も同様な問題が生じる。こうした課題に直面しないためにも、SoCはシステム・レベルの設計が必須となる。

インターコネクト性能が従来の最大2倍に

「Qsys」は、FPGAを使ったSoC開発を行うための生産性向上ツールであり、現行の「SOPC Builder」の後継ツールとなる。QsysはFPGAに最適化されたスイッチベースのネットワーク「Network-on-a-Chip(NoC)」アーキテクチャを基本としている。このために、メモリーマップおよびデータパスのインターコネクトの性能が、SOPC Builderと比較して、動作周波数を最大2倍も向上させることができる。また、Qsysは階層設計をサポートしており、システム・レベルのデザイン生産性が向上し、設計資産の再利用が容易となる。

上記以外にも、Qsysは下記のような特徴がある。

- Qsysは、従来のSOPC Builderで生成されたデータに対する互換性を提供するため、HDLで仕様を記述することなくFPGAをインテグレーションすることができる。

- 複数のバスマスタを使用している時も、高効率・低レイテンシーである。

- 64ビットのアドレス空間を持つとともに、階層設計が行えるため、モジュール単位でチームベース開発が可能である。

- デバッグ機能として、ホストPCからターゲットのバスにアクセスする機能(システムコンソール)やシミュレーションモデル(バスファンクションモデル)をサポート。

Qsysを利用することで、アルテラがこれまでサポートしてきたインターコネクト・ファブリック「Avalon」に加えて、AHB/AXI仕様のAMBAなど、業界標準のオンチップバスもFPGA上で混載して利用することが可能となる。Qsysの詳細については、改めてこのコーナーで紹介することにしたい。

これまで前編と後編の2回にわたり、組み込み開発の現場で抱える課題と、その対策について紹介してきた。FPGAが組み込み開発において、いかに有用なデバイスであり、開発のニーズに対応しているかをご理解いただけたであろうか。次回から、用途別にもっと最適なFPGAを選択するための方法について紹介する。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

●AN 417: C2H コンパイラによるファンクションの高速化: チェックサム付Scatter-Gather DMA

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。