第37回 システム統合を可能にする最新開発ツール(後編):FPGA Insights

FPGAの主なベンダーは、回路設計の大規模化に向けて、新しいチップの開発と同時に、システム統合を行う際の生産性を高める次世代開発ツールの開発にも力を入れている。後編では、アルテラの「Quartus® II 」で利用できるシステム・レベルの統合ツール「Qsys」を例に、複雑なFPGA設計を克服するために有効となる開発ツールの機能について解説する。

大規模な回路設計を行う場合、一般的にチップの内部を「標準IPコア」、「グルー・ロジック」、「カスタム・ロジック」と大きく3つのブロックに分けることができる。標準IPコアには「UART」や「メモリ・コントローラ」などがあり、共通IPコアとしての再利用が容易である。グルー・ロジックは、回路ブロック間を接続するためのロジック回路で、アドレスラインやデータライン、バス幅調整ロジック、アビトレーション・ロジックなどの接続機能が含まれる。それ以外がユーザー独自の機能を実現するためのカスタム・ロジックとなる。

この中で、特定の規格に準拠した標準IPコアは、独自に回路を設計しても差異化するのが難しい。このため、すでに開発済みのIPコアがシステム仕様を満足させるものでれば、そのIPコアを再利用した方が得策である。また、回路ブロック間を接続するためのロジック回路も、開発ツールの機能を使い自動で最適化することができれば、設計者の負荷を軽減することができる。このような開発環境を構築できれば、回路設計者はシステムの差異化につながるカスタム・ロジックの開発に、より多くの開発リソースを投入することが可能となる。

「IPコア再利用」「階層設計」「検証時間短縮」

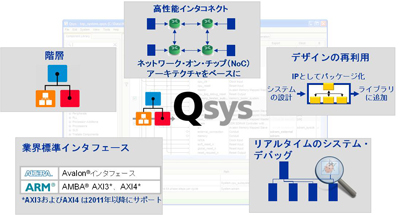

Qsysは、設計の生産性を向上させるために、「システムの階層設計」、「高性能なインタコネクト」、「IPコアの再利用」、「業界標準インタフェースのサポート」および「リアルタイムのシステム・デバッグ」などの機能を、さらに充実させた(図1)。例えば、Qsysでは100を超えるQsys準拠IPコアをライブラリとして用意している。Qsys準拠IPコアとは、アルテラが規定するIPコア製品としての要件に準拠した製品で、ドキュメントやデータ、リファレンスデザインなどが含まれる。AMBA AXIインタフェースなど、業界標準インタフェースに対応したサードパーティ製IPコアであっても、上記の要件に準拠した製品であれば、Qsys準拠IPコアとして取り扱われている。

Qsys準拠IPコアの中には例えば、PCI Expressなどの「インタフェース・プロトコルIP」、DDR/DDR2/DDR3 SDRAMなどの「メモリIP」、スケーラ、デインタレーサおよびアルファ・ブレンディング・ミキサなどの「ビデオ/画像処理(VIP)IP」、Nios® IIなどの「プロセッサIP」、JTAG、UART、SPI、RS232などの「組み込みIP」がある。これまでアルテラが提供してきたシステム開発ツール「SOPC Builder」でサポートされているほとんどの準拠IPコアも、Qsysで利用できるよう、アルテラで移行作業が進められている。サードパーティ製IPコアも含めて、Qsys準拠IPコアの種類はさらに拡充される予定である。

IPコアを再利用できれば、回路設計の生産性を高めることはできるが、回路が大規模になればなるほど、IPコア同士を正しく接続するのが大変な作業となる。特に異なるバス幅のIPコア同士を合わせ込んだり、割り込みの優先度を変更したりするときに、多くのIPコア間で数百の信号線やバスラインを接続しなければならない。こうした単純作業は、人手で行うとエラーを起こす確率が高くなる。

統合作業を自動化

このような課題に対して、Qsysは統合作業の一部またはすべてを自動化することで対処した。Qsysでは、直感的に使えるGUIを提供しており、IPコア間をどのように接続するかを指示すれば、Qsys側でインタコネクトの情報をHDLの形で自動生成してくれる。つまり、設計者が細かな統合作業を手作業で行わなくても、マウスを一回クリックするだけで、異なる回路ブロック間を接続することができる。このような統合作業の自動化はこれまでのSOPC Builderでもサポートされているが、Qsysでは階層設計にも適用できるよう、機能が強化されている。

しかも、FPGAに最適化されたスイッチベースのネットワーク「Network-on-a-Chip(NoC)」アーキテクチャに基づくQsysインタコネクトは、パイプライン・レジスタの数を調整することで、SOPC Builderを使った場合に比べて、動作周波数を最大2倍に向上させることができる。具体的には、タイミング解析の結果に基づき、インタコネクトの動作周波数をさらに高めたければ、「インタコネクト・パイプラインのステージ制約」という画面を表示させ、設計者が設定値を「高速」、「中速」、「低速」などに変更するだけでいい。あとは、より高い動作周波数が得られるように、ツール側でパイプライン・レジスタを自動挿入する。

システム・レベルの統合作業において、設計者を悩ませるのが性能改善におけるパイプライン化作業の煩雑さである。Qsysは、統合作業の自動化により、レイテンシと動作周波数のトレードオフを図りながらパイプラインを自動設計し、設計仕様に基づく性能改善を短時間で行うことができる。この結果、設計効率を大幅に改善することが可能となった。

IPコアの再利用

設計の生産性を向上するためには、サードパーティなどが開発し、すでに多くのICに組み込まれているIPコアを再利用するのが最も手っ取り早い。しかも、そのIPコアが標準インタフェースを備えていれば、システム統合を行う際に、チップ固有のインタフェースに合わせ込むために必要な再設計の手間を省くことができる。

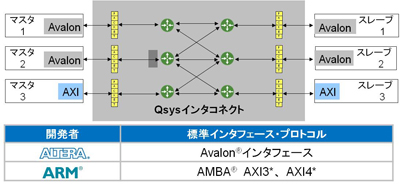

標準インタフェースとしては、ARMの「AMBA AXI」や「AMBA AHB」などが有名だが、アルテラでは「Avalon」を提供している。Qsysでは、さまざまなインタフェースの組み合わせをサポートしていく予定である(図2)。アルテラは次世代のFPGAで、ARMアーキテクチャのプロセッサコアを、ハードコア、ソフトコアの両方でサポートしていく計画がある。それと並行して、2011年以降には「AMBA AXI3」や「AMBA AXI4」のサポートが予定されている。

IPコアは市場で流通しているサードパーティ製だけではない。特に日本の電子機器メーカーは、自社内で独自に開発した設計資産を大量に保有しているといわれている。こうした社内の設計資産をIP化し再利用していくことも、システム・レベルの回路設計で生産性を高めるには重要となる。Qsysは、ユーザー固有のRTL設計データをQsysのライブラリとして取り込むためのコンポーネント・エディタ・ツールを提供している。ユーザーは、QsysのGUIウィザードを利用して、ユーザー固有のRTL設計データを自動的にパッケージ化する。その上で、再利用可能なIPコアとしてコンポーネント・ライブラリに登録することができる。このとき、IPコアをパラメタライズすることができる。例えば、FFT演算用のIPコアであれば、1種類のライブラリでありながら、タップ数を指定することで、用途に最適な回路を生成できるようになる。これらの機能は従来のSOPC Builderでもサポートされていたが、Qsysではさらに、新たに登録されたIPコアを含め複数のIPコアを統合したサブシステムとして登録することができる。これによって、設計の抽象化レベルはさらに高まることになる。

検証サイクルを短縮

ICの集積度が高まり、高機能化するにつれ、設計した回路の検証作業は、全体の設計フローの中でも、多くの時間を要する工程となっている。このため、設計の手戻りを少なくし生産性を向上させるために、設計の上流工程での検証作業がより重要となりつつある。

Qsysでは、設計者が「BFM(バス・ファンクション・モデル)」や「モニター」といったテスト環境を利用することができる。標準でマスター/スレーブBFMやモニターなどの検証用IPスイートが提供されており、設計者がわざわざBFMを開発する必要はない。さらに、QsysはHDLの形でシステム用のテストベンチを自動で生成するため、テストベンチ作成のための工数や専門エンジニアも不要となる。

またJTAGあるいはTCP/IPのブリッジIPが用意されており、これを、FPGA内に組み込んでおけば、外部からハードウエアの検証が容易に行えるオンチップ・デバッグ機能を利用することができる。これにより、Qsysのシステム・コンソールから、ブリッジIPを介して機能ブロックのポートにアクセスし、外部からコマンドを送ったり、レジスタの状態を読み出したりすることができる。このため、レジスタの設定を手作業で行っていたときに比べ、検証作業の効率を大幅に改善することができ、ボード完成までの期間を短縮することができる。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

●FPGA システム設計における、ネットワーク・オン・チップ・アーキテクチャの利点

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。