第36回 システム統合を可能にする最新開発ツール(前編):FPGA Insights

システム・レベルの回路を、1つのチップに集積する動きはとどまることを知らない。それはスマートフォンに代表されるように、小型・軽量、低消費電力で高機能な機器を実現するために必須となるからだ。いまや複数のプロセッサコアや大容量メモリをはじめ、周辺のデジタル回路やさまざまなインタフェース回路をワンチップに集積することができる。このようなシステム統合を効率よく実現するのが最新の開発ツールである。前編では、システム統合の開発ツールが重要となる背景として、FPGAにおける設計規模の増大と、それに伴う設計生産性の改善のための対応について概略を述べる。

半導体チップの高集積化や高機能化の動きはASICやASSP、カスタムLSIだけでなく、FPGAでも同様だ。集積度の推移がそれを明確に示している。例えば、アルテラのFPGA「Stratix®シリーズ」は、約10年間でロジック容量が13倍以上に増加している(図1)。このような回路設計規模の増大に対して、設計者の数は比例して増えていない。それどころか、固定費削減の影響で、設計者の数は縮小している企業もあるようだ。つまり、半導体チップの高集積化や高機能化の要求に対して、最もプレッシャーを受けているのが回路設計者である。

こうした中で、開発サイクルを短縮しつつ、期待される開発成果を得ようとすれば、設計の生産性を向上していくしかない。そのためには、「設計の抽象化レベルを上げる」ことや「設計資産の再利用」、「検証作業の効率化」を行っていくことが有効な手段となる。

“生産性”と“設計の抽象度”

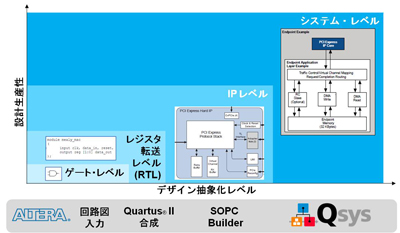

ここで、FPGAにおける設計の生産性と抽象化レベルについて、その歴史を振り返ってみる(図2)。FPGAが登場した1990年代初頭の論理ゲート規模は、せいぜい数百ゲートであり、回路図入力によるゲート・レベルの設計が一般的であった。その後、RTL(レジスタ転送レベル)設計が普及し、HDL(Hardware description language)で記述された機能を論理合成するツールが登場した。ASICの設計では1990年代前半からRTL設計の流れが加速し、FPGAでも1995年ごろからRTL設計へと移行していった。EDAベンダーからもさまざまな論理合成ツールが商品化され、本格的なRTL設計の時代を迎えた。アルテラでも、こうした流れに沿って2000年代に入り開発ツール「Quartus® II 」で論理合成機能のサポートを始めた。

しかし、半導体プロセス技術が進化し、実装可能な回路規模がさらに大きくなると、RTL設計でもその効率は下がり、開発期間と開発コストが問題となってきた。このため、1990年代後半から2000年ごろにかけて、IPコアを利用したIPレベル設計が注目され始めた。IPコアとは大規模な回路を構成するための部分的な設計済み回路情報で、ある特定の機能を備えた回路ブロックのことである。当時、その代表的なものとしてPCIバス・インタフェースのIPコアなどがあった。特に、インタフェース系など、特定の規格に準拠した仕様が求められる回路ブロックは、IPコア化が進んだ。

FPGAベンダーなどでも、自社チップ向けに「機能マクロ」などと呼ぶIPコアをライブラリとして準備してきた。これによって、回路設計者はサードパーティから供給されるIPコアも含めて、設計ツール上でさまざまなIPコアを再利用することが容易になった。RTLからIPレベルへと設計の抽象化レベルを上げていくことで、IC設計の生産性は格段に向上することとなった。

サードパーティ製のIPコアを活用するメリットはもう1つある。標準化された回路ブロックを外部から調達することで、回路設計者は他社と差異化するために必要となる機能ブロックの開発に、設計資源を集中することができるようになるためだ。FPGA設計においては、2000年代半ばからIPコアの活用が広まっていった。

システム統合と開発環境

設計の生産性を向上させるためには、IPコアの再利用が有効な手段の1つであることを疑う余地はなかった。このころからASICユーザーの間にも、自社開発した設計資産をIPコア化して、再利用する動きも本格化した。しかし、複数のIPコアを使ってシステム統合を行う上で、1つの課題が浮上していた。すぐれたIPコアを市場で調達しても、それらのIPコアを組み合わせ、システム・レベルに統合していくための最適なツールが少なかったことだ。

PCIバス・インタフェースなどのチップ間のインタフェース仕様が規格化されているIPコアの場合も、チップ内部の接続仕様はほとんど標準化されておらず、IPコアごとにばらばらに規定されていた。このため、市場に流通している汎用的なIPコアを調達しても、チップ内部の接続部分の設計はユーザー自身で行うしかなく、当時の回路設計者はその設計に多大な労力を強いられてきた。つまり、実際の回路設計で第三者が開発した多くのIPコアを再利用するには「接続仕様を合わせ込む」という、かなり高いハードルを越えなければならなかったというわけだ。

FPGAベンダーは、2000年ごろからプロセッサを内蔵できるFPGA製品を発表した。システム・レベルの回路をワンチップで実現するためである。一般的にプロセッサでは、周辺回路とデータをやり取りするための内部バス仕様が決められている。その代表例としてARM社が提唱したバス規格「AMBA」や、アルテラがサポートする「Avalon」などがある。

アルテラではプロセッサを内蔵できるFPGA製品の発売に合わせて、Quartus IIで利用できるシステム開発ツール「SOPC Builder」を用意した。このSOPC Builderは、Avalonをベースとしたもので、各種のIPコアを効率よく統合するための仕組みを備えている。開発ツールが進化したことによって、IPコアを再利用してシステム統合を行う際の大きな課題を解決することができた。

図1に示したように、FPGAは1つのチップに統合できる回路規模が今後も増大していくものとみられている。設計者の立場から見れば、設計の抽象化レベルをもう一段高めて行かなければ、生産性を向上するどころか、維持することさえできなくなる可能性も否定できない。つまり、複数のIPコアを組み合わせた複雑なシステム・レベルの回路ブロックまでIPコアとして扱えるような、機能拡張された開発ツールが必要となってくる。

設計の抽象化レベルをシステム・レベルに引き上げていくためには、開発ツールにどのような機能が必要となるのであろうか。主な要件を列挙すると「IPコアの再利用が容易であること」、「システム・レベルの設計を階層的に行えること」、「検証時間を短縮できること」、などが求められている。これらの要件に対応した開発ツールの1つが、Quartus IIで利用できるシステム・レベルの統合ツール「Qsys」である。上述した要件を満たすことで、複雑なFPGA設計においても、生産性を向上することが可能となる。

前編では、FPGAにおける設計規模の増大と、それに伴う生産性の改善について概略を述べた。システム・レベルの回路設計/統合を行おうとすれば、生産性の点で従来のIPレベル設計ですら、その対応が難しくなりつつある。後編では、Quartus IIで利用できるシステム・レベルの統合ツール「Qsys」を例に、IPコアの再利用、階層設計、あるいは検証時間を短縮するための機能、などについて解説する。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

●FPGA システム設計における、ネットワーク・オン・チップ・アーキテクチャの利点

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。