第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜:FPGA Insights

FPGAの主要ベンダーは、回路設計の大規模化に向けて、新しいチップの開発と同時に、システム統合を高い生産性で行うことができる次世代開発ツールの開発にも力を入れている。さらに、組み込みシステム用途ではハードウェア設計に加えて、内蔵するプロセッサ用のプログラム開発を効率よく行うためのツール提供が必須となる。

Qsys:システム・レベル設計で生産性向上

最新の半導体チップは、複数のプロセッサコアや大容量メモリをはじめ、大規模なシステム・レベルの回路を1つのチップに集積することが可能となっている。こうした中で、FPGAは、このシステム・レベル設計を効率よく行える半導体ソリューションの1つとして注目されている。これを可能とするのは、最先端プロセス技術を駆使したFPGAチップと、SoC設計に最適なツールの提供である。

SoC設計の生産性を向上させるためには、設計の抽象化レベルをシステム・レベルに引き上げていくことが重要となる。そのためには、「IPコアの再利用が容易であること」、「システム・レベルの設計を階層的に行えること」、「検証時間を短縮できること」、といった要件が開発ツールに求められている。

2011年11月に横浜で開催された「Embedded Technology 2011」(ET2011)でも、こうした要件を満たす最新の開発環境が来場者の注目を集めていた。例えば、アルテラ・ブースでは、開発ツール「Quartus® II」で利用できるシステム・レベルの統合ツール「Qsys」を紹介した。Qsysでは、これまでアルテラが提供してきたシステム開発ツール「SOPC Builder」の機能に加えて、「業界標準インタフェースのサポート」、「階層構造設計」、「リアルタイムのシステム・デバッグ」、「IP管理機能」などが提供される。

システム・レベル設計の生産性を向上するための1つの手法は、流通しているIPコアを最大限に活用することだ。しかも、そのIPコアが標準インタフェースを備えていれば、システム統合を行う際にインタフェース部の再設計といった手間を省くことができる。Qsysは、これまでアルテラが提供してきた「Avalon」に加えて、ARMの標準インタフェースである「AMBA AXI」のサポートが始まっていることに加え、「AHB」のサポートも検討している。しかも、1つのチップ内にAvalonとAMBA AXIを混載して実装することができる。これによって、多くのIPコアの再利用が容易となる。

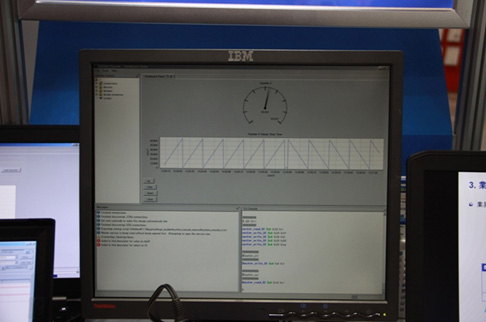

また、FPGA内にJTAGあるいはTCP/IPのブリッジIPを組み込んでおけば、外部からハードウェアの検証が容易に行えるオンチップ・デバッグ機能を持たせることができる。これにより、Qsysのシステム・コンソールから、ブリッジIPを介して機能ブロックのポートにアクセスし、外部からコマンドを送ったり、レジスタの状態を読み出したりすることができる。従来はレジスタの設定を手作業で行っていたが、オン・デバッグ機能により、ボード完成までの期間を短縮することができる。これらの検証機能により開発の効率を大幅に改善することができる(写真4)。

これ以外にも、Qsysはチーム・ベースの設計をサポートする階層構造設計への対応や、パイプライン・レジスタを自動で挿入することにより、従来に比べ最大2倍の動作周波数が得られるQsysインタコネクト技術をサポートしており、こうした新たな機能を活用することで、SoC設計の生産性をさらに向上させることができる。

Virtual Target:実機レスでソフトを動作検証

組み込みシステム設計者の間では、SoC FPGAに対する期待が日増しに高まっている。それは最新のマルチコア・プロセッサをハードウェアで実装したFPGAが市場に投入されるからだ。これによって、設計者はSoCとしての十分なコストパフォーマンスを手に入れやすくなった。

例えばアルテラは、組み込みシステムの開発者に向けた取り組みとして「エンベデッド・イニシアチブ」を2010年10月に発表した(参考:EE Times Japanの記事)。この構想を実現するために、ハードウェア化されたARMプロセッサや高速インタコネクトのサポート、ハードウェア設計環境およびソフトウェア開発環境の整備などに取り組んできた。そして1年後の2011年10月にはARMベースの「SoC FPGA」ファミリとそのシミュレーション・モデルが発表された(参考:EE Times Japanの記事)。

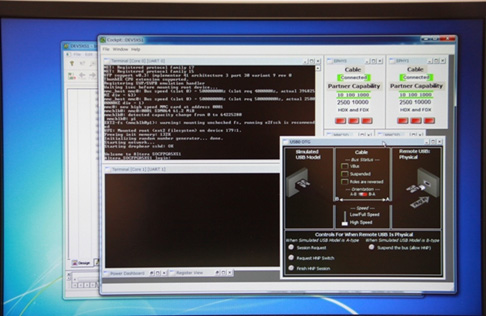

SoC FPGA開発ボードを仮想化したパソコンベースの機能シミュレーション・モデル「SoC FPGA Virtual Target」は、デュアルコアのARM Cortex-A9 MPCoreプロセッサとその周辺機能をモデル化したものとなる。DDR SDRAMやフラッシュメモリ、バーチャルI/Oなど、ボード・レベルのコンポーネントもモデル化されて内蔵されている。SoC FPGA開発ボードに実装された主なコンポーネントのデバイス・ドライバも含まれているため、実機が完成していない状態でも、Virtual Targetを用いれば比較的容易にソフトウェアの動作検証が可能となる。また、Virtual Target上では、「Linux」や「VxWorks」といったOSを起動させることもできる。写真5はLinuxの起動画面である。会場では、サポートが始まったばかりのVxWorksベースのシミュレーション環境も紹介された。

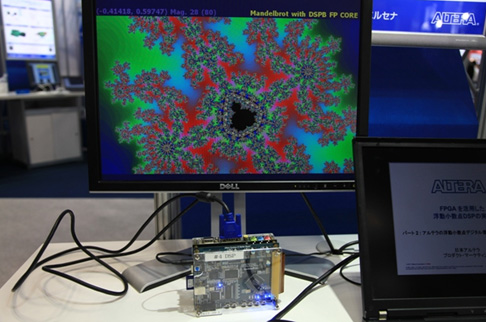

DSPソリューション:シングル・チップで1T FLOPS超

FPGAによるDSPソリューションも大きな進化を遂げている。最新のFPGAに浮動小数点演算機能を実装した場合、演算性能はシングル・チップで1T FLOPSを超えることもある。MPUやDSPに比べて演算性能が10〜100倍も優れ、演算性能がFPGAと同等の汎用GPUと比較すれば、消費電力は1/4以下となる。その上、FPGAは浮動小数点演算機能も含めてシステム・レベルの機能をワンチップに集積できる。会場では、Cyclone® IIIスタータボードを使い「Mandelbrot」の演算とその描画デモを行った(写真6)。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

●次世代組込みシステム向け、カスタマイズ可能なARM ベース SoC FPGA

●FPGA システム設計における、ネットワーク・オン・チップ・アーキテクチャの利点

●アルテラのFPGA浮動小数点DSPデザイン・フロー〜第三者機関による分析〜

●DSP 設計を加速させるトータル28nm DSP ポートフォリオ

●Stratix V 可変精度DSP ブロックによる高性能DSP アプリケーションの実現方法

●Arria V またはCyclone V 可変精度 DSP ブロックによる高性能DSP アプリケーションの実現

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。

写真4:オンチップ・デバッグ機能により、データをリアルタイムに解析することができる

写真4:オンチップ・デバッグ機能により、データをリアルタイムに解析することができる 写真5:製品の早期市場投入を実現するVirtual Target

写真5:製品の早期市場投入を実現するVirtual Target 写真6:Cyclone III スタータボードで「Mandelbrot」を演算し描画した

写真6:Cyclone III スタータボードで「Mandelbrot」を演算し描画した