第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜:FPGA Insights

FPGAは、組み込みシステムの設計/開発に深い関わりを持つようになった。2011年11月に横浜で開催された「Embedded Technology 2011」(ET2011)では、最新のFPGA製品でサポートされている高速シリアル通信技術や並列処理技術、SoC技術、ハードウェア/ソフトウェア開発環境などが来場者の関心を集めた。本稿では、アルテラ・ブースに展示されたFPGAの注目技術について取り上げる。

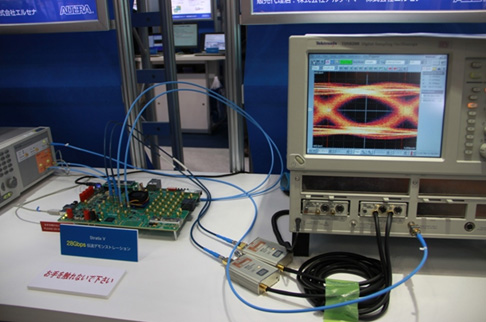

高い信号品質の28Gbpsトランシーバ

28nmの最先端プロセスで製造されている最新のFPGAは、高い性能や機能を実現しつつ、消費電力やシステムコストの低減を図っている。また、製品のバリエーションも豊富で、設計者はアプリケーションにより最適なデバイスを選択することが可能となった。一例だが、アルテラは28nm FPGAとして、ハイエンド製品向け「Stratix® V」、ミッドレンジ製品向け「Arria® V」、ローエンド製品向け「Cyclone® V」を用意している。

こうした28nmFPGA製品の特徴の1つは高速トランシーバがサポートされていることだ。例えば、「Stratix V」は、14.1Gbpsから28Gbpsで動作する、最大66個の全二重トランシーバ・チャネル(フィジカル・メディア・アタッチメントとフィジカル・コーティング・サブレイヤ)を備えている。

ET2011会場では、データレート28Gbpsのトランシーバを内蔵したStratix Vが実装された評価ボード(SI開発キット)を使い、トランシーバからの出力信号を取り出して、デジタルオシロスコープの画面にその波形をアイパターンで表示した(写真2)。この波形から、データレートが28Gbpsでも高い信号品質で送信されていることが見て取れる。

最新の通信インフラ向け装置では、既に100Gbpsクラスのデータレートが要求されている。この要求に対して現在は、10Gbpsのトランシーバを10レーン使って100Gbpsのデータレートを実現している。ところが、Stratix Vがサポートしている28Gbpsのトランシーバを用いれば、100Gbpsのデータレートを実現するのに4レーンで済む。

この場合、28Gbpsトランシーバを4レーン利用した方が、10Gbps×10レーン構成と比べて消費電力やシステムコストを削減できるという。10GbpsトランシーバIPのみで消費電力を比較しても、今回の28nm製品は現行の40nm世代品に比べて半減している。

前述の通り、アルテラは28nm製品として、ハイエンド製品向け「Stratix V」、ミッドレンジ製品向け「Arria V」、ローエンド製品向け「Cyclone V」のFPGAを用意している。サポートするトランシーバの性能でみれば、データレートが最大28Gbpsのトランシーバを内蔵することができるStratix Vに対して、Arria Vでは最大10.3Gbps、Cyclone Vでは最大5Gbpsをそれぞれサポートしている。つまり、用途に応じてFPGAファミリを選択すれば、システムの性能やコストを最適化できるというわけだ。

これ以外にも、Qsysには次世代SoC FPGA設計に必要な機能がいくつか追加されている。その1つが、階層構造設計のサポートである。この機能により、IP機能のコレクションをサブシステムとして再利用しやすくなり、大規模なシステム開発やスケーラブルなシステム拡張がこれまで以上に容易に行えるようになる。

また、業界標準のバス・インタフェースをサポートしていることである。最新のQuartus® II 開発ソフトウェアでは、アルテラがこれまでサポートしてきたインターコネクト・ファブリック「Avalon」に加えて、「AMBA AXI」など、業界標準のオンチップバスにも対応しており、さまざまなバス仕様のIPコアをFPGA上で混載して利用することが可能となる。

1080p/30fpsのビデオ解析をシングル・チップで実現

FPGAの利用が期待されている分野の1つに、高解像度の映像/画像信号をリアルタイムに処理し、解析するアプリケーションがある。ハードウェアによる並列処理に適したFPGAの強みを生かすことで、ローエンドFPGAであっても高精細な画像による監視システムを実現することができる。

ET2011会場でデモ展示を行った交通監視アプリケーションは、その代表例である(写真3)。このシステムは、Cyclone IVをベースとしたもので、並列アルゴリズムとマルチコア・アーキテクチャを備えたEutecus社のマルチコアビデオ解析エンジン(MVE)IPが実装されている。

このシステムの特徴は、1080p/30fpsのフルHD解像度でリアルタイム画像処理を行うのに必要な性能を実現することができることだ。また、最大9つのイベントを掛け合わせて、画像を解析することができる。こうした解析処理をDSPとソフトウェアの組み合わせで行う場合、これまではかなり高性能なDSPを用いるか、チップを複数個使う必要があった。このため、放熱対策が必要であったり、実装スペースが大きくなったりするため、組み込みシステムとしては課題となっていた。それが、Cyclone IVとMVE IPを組み合わせて使うことにより、高画質で複雑なビデオ解析をシングル・チップで、しかも比較的安価に実現することができるようになった。

会場では、ラウンドアバウトと呼ばれる交差点や高速道路のインターチェンジなどで撮影されたフルHD映像を用い、交差点に進入する自動車などに対して、事故の危険性の検知、赤信号違反の検出、歩行者の検出などを行うビデオ解析のデモを行った。

このビデオ解析ソリューションでは、システム開発者が事象検出用のパラメータとルールをGUIで設定する。これによって、例えば雨や雪など気象条件による画質劣化を補正したり、画像の形状などによる物体の認識(大型車、普通車、人間など)をしたり、ある空間における移動方向や速度を認識したりすることができる。さらに、複数の事象検出結果を組み合わせて演算すれば、事故の危険性のある車両や信号無視の車両を検出して、その車両を指定した色(赤や緑)の枠で囲むなど、画面上で分かりやすく表示させることができる。

これまでのDSPベースのソフトウェア処理の場合、解像度720pかそれ以下の画像で、2〜3イベントを掛け合わせるビデオ解析であれば、対応することはできた。しかし、今回のようなフルHD画像で、かつ高度なビデオ解析を行えるのは、並列処理を得意とするFPGAの強みであろう。しかも、シングル・チップで実現できるため、小型監視カメラなどの組み込みシステムにもその応用が広がる。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。

写真2:28Gbpsトランシーバの出力波形のアイパターン

写真2:28Gbpsトランシーバの出力波形のアイパターン 写真3:MVE IPを実装したCyclone IV で、交差点における交通監視を行うデモの模様

写真3:MVE IPを実装したCyclone IV で、交差点における交通監視を行うデモの模様