第31回 「ARM搭載 FPGA によって格段に広がる SoC 開発の選択肢」(後編):FPGA Insights

SoCに対するシステム設計者のニーズはさまざまである。また、最先端プロセスを用いたSoC設計では、前編で述べてきたように、いくつかの課題を抱えている。FPGAベースのSoC設計を提案するFPGAベンダーでは、こうしたシステム設計者のニーズに対応する製品や開発ツールを用意している。本稿(後編)では、その一例としてアルテラが提供しているSoC FPGAソリューションについて解説する。

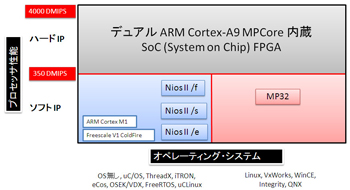

システム設計者が、SoCに搭載するプロセッサに関する要求事項として、「高性能」と「ソフトウエア資産の再利用」という大きな流れがある。こうしたSoC設計の要求に対して、アルテラは2つのアプローチを取っている。高性能の方向性に対しては、ARM社の「Cortex-A9MPCore」プロセッサをハードコア・プロセッサとして搭載したFPGAを用意していく予定である。

ソフトウエア資産の再利用に対しては、主なOSに対応したソフトコア・プロセッサをサポートすることにしている。現在、自社開発のソフトコア・プロセッサ「Nios II 」ではμITRONやμCLinuxなどのOSに対応しているが、組み込み市場には様々な組み込みシステムで標準的に採用されているWindriver社の「VxWorks」や組み込み用のLinux系の各種OSのニーズが多い。しかし、新たにそれらのOSをNios IIに移植するのでは時間とコストがかかる。そのため、すでにこれらのOSがサポートされているMIPS社のMIPS32アーキテクチャにもとづくソフトコア・プロセッサMP32を同社のFPGAでサポートしていく方針を打ち出した。また、マイコン・クラスのソフトコア・プロセッサとしては、Nios II以外にARM社のCortex-M1コアとFreescale社のColdFire v1コアが各ベンダーにより提供されている。(図1)。

普及のカギを握る開発ツール

第2世代のSoC FPGAが広く市場に受け入れられるためには、SoCチップとして求められる機能と性能の実現やコストの低減は重要である。それと同等かそれ以上に大切なのが、SoCを設計するための使いやすい開発環境を用意していくことである。SoC設計者にとって、新しいチップでSoCを設計するために、新たな開発ツールを導入してその操作方法を習得したり、複数の開発ツールを使い分けたりすることは大変な作業となる。使い慣れた開発ツールに拡張機能を追加するだけで、新たな開発環境を構築することができれば、SoC設計のための労力を大幅に軽減することができる。

FPGAベンダーはこうした課題に対して、既存の開発ツールを生かしつつ、新たな機能を追加することで、現行のFPGA設計はもとより、SoC FPGAにも対応できる開発ツールを用意しようとしている。その一例として、ここではアルテラの取り組みを取り上げる。

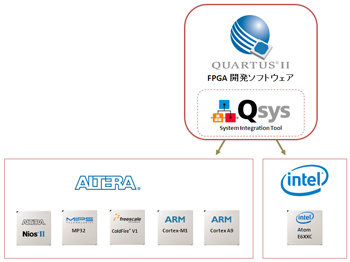

アルテラは、単一のFPGA設計フローに基づくマルチベンダー、マルチプロセッサ・アーキテクチャのSoCプラットフォーム開発を目指した「エンベデッド・イニシアチブ」を2010年10月に発表した。アルテラのFPGA設計フローの手法は、自社製のソフトコア・プロセッサ「Nios II 」と他社製のソフトコア・プロセッサIPによるSoCソリューションに加え、新たにサポートを予定しているARMコア(ハードコア)、MIPSコア(ソフトコア)などを含めた形で、単一のFPGA設計フローに基づいたシステム統合ソリューションを提供していくことである。

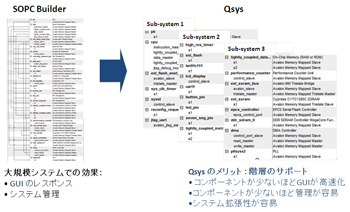

設計フローの中核となるのが、FPGA開発ソフトウエア「Quartus II 」である。今回このQuartus IIにシステム・レベル統合ツール「Qsys」を追加した。Qsysは、現行の「SOPC Builder」の後継ツールとなるもので、FPGAに最適化されたスイッチベースのネットワーク「Network-on-a-Chip(NoC)」アーキテクチャを採用している。QsysはIP(Intellectual Property)コアとサブシステムを接続するインタコネクト・ロジックを自動的に生成することができるため、SoC FPGAの設計期間を短縮し、労力の軽減を可能とする。また、Qsysはパイプライン・レジスタの自動挿入を可能とする機能を備えており、SOPC Builderに比べて、最大2倍の動作周波数を実現することができる。

これ以外にも、Qsysには次世代SoC FPGA設計に必要な機能がいくつか追加されている。その1つが、階層構造設計のサポートである。この機能により、IP機能のコレクションをサブシステムとして再利用しやすくなり、大規模なシステム開発やスケーラブルなシステム拡張がこれまで以上に容易に行えるようになる(図2)。一般的なEDAツールで行われているようなチームベースの開発にも有効である。

2つ目がリアルタイムのシステムデバッグである。検証用IPとシステム・コンソールを使って、ボード開発までの期間を短縮することができる。この機能を使えばシステム・コンソールからブリッジIPコアを経由して、Qsysシステムにリード/ライト・トランザクションを送信し、リアルタイムでシステムにアクセスすることができる。

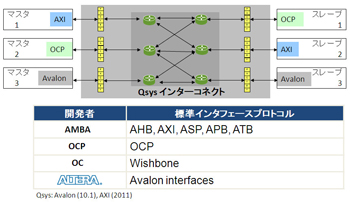

3つ目は業界標準のバス・インタフェースをサポートしていることである。Quartus II 開発ソフトウエアv10.1では、アルテラがこれまでサポートしてきたインターコネクト・ファブリック「Avalon」に加えて、AMBAのAHBやAXIなど、業界標準のオンチップバスにも対応することにしており、さまざまなバス仕様のIPコアをFPGA上で混載して利用することが可能となる(図3)。

SoC設計に用いられるIPコアは、内部接続するためのバス仕様がさまざまである。SoC設計において同じバス仕様のIPコアのみを使って集積する場合は問題がないが、異なるバス仕様のIPコアを組み合わせて同一チップ上で混載しようとすると、両者を接続するためのブリッジ機能が必要となる。システム設計者がこのブリッジ回路を開発するには大きな負担となる。

Qsysは、このようなバス仕様の違いを吸収する仕組みを備えている。この仕組みによって、システム設計者は、IPコア固有のバス仕様を意識することなく、回路設計に必要なIPコアを自由に組み合わせることができる。つまり、QsysはSoC FPGAを容易に設計するためのコア技術の1つといえる。

Qsysを用いることで、Nios IIやCortex-A9MPCore、MIPS32アーキテクチャのプロセッサ・コアを内蔵したFPGAはもとより、Intel社のAtomプロセッサとFPGAを統合した「E6xxC」プロセッサも、開発フローを共通化することが可能となる。もちろん、アルテラのQsysを用いるシステム統合の設計フローは、プロセッサを実装していないFPGAの設計にも適用することができる(図4)。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。