第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜:FPGA Insights

FPGA製品が究極のデバイスに近づきつつある。最新のFPGAでは、システム全体の動作を停止させることなく、チップ内の回路ブロックの一部をダイナミックに再構成することができる。本稿では、その一例としてアルテラの28nm FPGAでサポートされている「パーシャル・リコンフィギュレーション」機能と、その設計方法などについて解説する。

回路の一部をダイナミックに変更

FPGAの特徴の1つは、設計の柔軟性である。応用製品が市場に投入された後でも、その回路(ハードウェア)の内容を電気的に書き換えることができる。しかも、微細加工技術の進展により、1チップに搭載できる汎用ロジック数や回路の規模は大きくなり、高性能なマイクロプロセッサ・コアやDSPブロック、メモリ・ブロック、高速トランシーバなども実装することができる。まさに、システムレベルの機能をワンチップに集積することが可能となった。

FPGAは設計者の手元で設計済みの回路を実装することが可能なため、システムの仕様変更などがあっても柔軟に対応することができるデバイスである。しかし、従来であれば、回路の再構成を行う場合に、システムの電源をいったん切らなければならなかった。これに対してパーシャル・リコンフィギュレーション機能は、FPGAのチップ上で同時に動作せず、かつ置き換え可能な機能ブロックを、回路の外にあらかじめ準備しておけば、必要に応じてその部分だけを置き換えることができる機能である。この結果、余分なコストをかけず、できる限り小さいチップサイズで、システムに最適な機能や性能をFPGAに実装することが可能となる。

既存の設計手法を活用

ここからは、アルテラのパーシャル・リコンフィギュレーション機能やその設計手法について説明する。設計ツールとしては、アルテラの開発ツール「Quartus® II」が対応している「インクリメンタル・コンパイル」手法と「LogicLock」フローの2つの機能を活用して設計することができる。

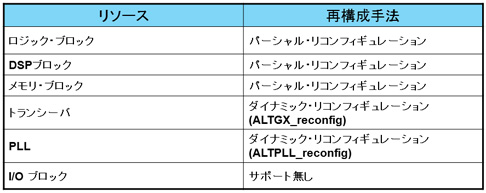

再構成が可能なリソースとその方法を表1に示す。アルテラはトランシーバとPLLに関して「ダイナミック・リコンフィギュレーション」という名称で、これまでもダイナミックな再構成をサポートしている。これらに加えて、今回の28nm FPGAでは「パーシャル・リコンフィギュレーション」という呼称で、ロジック・ブロックやDSPブロック、メモリ・ブロックといったコアロジックに関してもダイナミックな変更を可能とした。これにより、I/Oブロック以外は、ダイナミックに再構成することができるようになった。

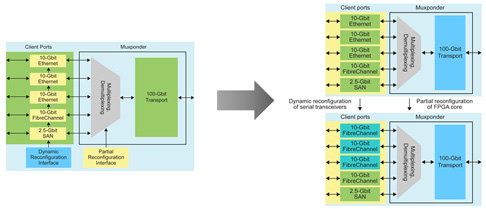

パーシャル・リコンフィギュレーション機能を活用できる用途として、インフラ系通信装置「OTNマックスポンダ」を挙げることができる。その例を図1に示す。OTNマックスポンダは、ファイバチャネルやSDI、イーサネット、SONETなど異なるプロトコル通信に対応しなければならず、複数のトランシーバ機能をダイナミックに切り替えられることは重要である。

モジュール・バウンダリを統一

パーシャル・リコンフィギュレーション機能を使ったシステムの設計を行うには、いくつかの準備が必要である。まず、Quartus II プロジェクトの作成である。具体的には、プロジェクトの各機能ブロック(インスタンス)のHDLファイルを作成し、リコンフィギュレーションの対象となる機能ブロック(パーシャル・ブロック)と、そうでない固定機能ブロックを選定する。そして、特定したパーシャル・ブロックは、インクリメンタル・コンパイル手法とLogicLockフローを使ってフロアプランを作成する。ここで特に注意しなければならない点がある。リコンフィギュレーションの対象となる機能ブロックを作成する際に、ビット幅やI/Oポート数などモジュール・バウンダリを統一しておく必要がある。

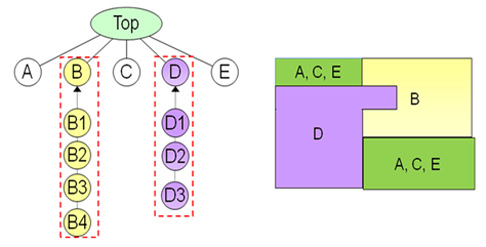

図2に再構成可能なデザインパーティションを2つ含んだトップ階層デザインを示す。ブロック「B」と「D」にはそれぞれ異なるロジック・ファンクション(B2、D3など)が含まれている。このケースではFPGAで実装できるデザイン・ロジックの組み合わせは12通りとなる。

コンパイルを行う際は、リコンフィギュレーション領域におけるアクティブなモジュールを作成する。必要に応じてコンパイル用に異なるモジュール構成のリビジョンを作成することとなる。最後に、チップ全体のプログラミング・ファイルおよび各パーシャル・プログラミング・ファイルが生成される。

PCIeやイーサネット経由でダウンロードも

設計データをコンパイルし、タイミング検証が完了すれば、プログラミング・ファイルをチップに実装する。その構成方法として大きく2つある。1つは外部ホストを利用する方法で、プログラミング・ファイルを格納した外部のコンフィギュレーション・メモリからダウンロードして、FPGA内部の回路を再構成する。もう1つは、FPGAに内蔵したプロセッサコア(例えばNios IIなど)を利用する方法で、外部のコンフィギュレーション・メモリから、対応するプログラミング・ファイルをロードして、FPGAを再構成する。

外部ホストを利用する場合、コンフィギュレーション・メモリとの接続はファスト・パッシブ・パラレル(FPP)モードがサポートされている。これに対してアルテラは、今後の新たな計画として、PCI Express(PCIe)やギガビット・イーサネット経由でプログラミング・ファイルをFPGAにロードすることも検討している。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

●次世代組込みシステム向け、カスタマイズ可能なARM ベース SoC FPGA

●FPGA システム設計における、ネットワーク・オン・チップ・アーキテクチャの利点

●アルテラのFPGA浮動小数点DSPデザイン・フロー〜第三者機関による分析〜

●DSP 設計を加速させるトータル28nm DSP ポートフォリオ

●Stratix V 可変精度DSP ブロックによる高性能DSP アプリケーションの実現方法

●Arria V またはCyclone V 可変精度 DSP ブロックによる高性能DSP アプリケーションの実現

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。

表1:リソースごとの再構成手法

表1:リソースごとの再構成手法 図1:ダイナミック・リコンフィギュレーション機能をOTNマックスポンダへ適用した例

図1:ダイナミック・リコンフィギュレーション機能をOTNマックスポンダへ適用した例 図2:再構成可能なデザインパーティションを2つ含んだトップ階層デザイン

図2:再構成可能なデザインパーティションを2つ含んだトップ階層デザイン