第38回 「先端FPGAにみるDSP実装の柔軟性」:FPGA Insights

「18ビット精度モード」か「高精度モード」を選べるアルテラFPGAのDSPブロック FPGAやDSPの既成概念を覆す「可変精度DSPブロック」がいま注目を浴びている。アルテラの28nm FPGAに内蔵されたこの革新的なブロックは、高精度信号処理向けのネイティブサポートと、FIRフィルタ、FFTなどの共通のDSP構造向けに最も効率的な実装の組み合わせを提供する。本稿では、ターゲット機器およびDSPアルゴリズムごとに乗算器の精度を変えられ、FPGAリソースを効率的に使える可変精度DSPブロックのメリットを探る。

3ファミリに共通するDSPアーキテクチャ

FPGAは、高い演算性能が求められるDSPのプラットフォームに用いられる(本稿で用いる「DSP」は、Digital Signal Processing:デジタル信号処理の意。Digital Signal Processorは「DSPプロセッサ」と表記する)。

数ギガMAC/s(1秒当たりの演算回数)なら市販のDSPプロセッサでも対応できるが、それ以上になるとハードウェアの特長である並列処理が効くFPGAが適していると言われる。特にサンプリング周波数が数十MHz以上、タップ長が比較的短いFIR(有限インパルス応答)フィルタやFFT(高速フーリエ変換)、DCT(離散コサイン変換)といったDSPアルゴリズム、データ変換を伴うデータパスの実装に使われることが多い。

一方、高精度な浮動小数点演算は専用DSPプロセッサが使われることがほとんどで、FPGAは固定小数点演算に限られることが多い。最適設計されたDSPプロセッサとソフトウェアの組み合わせに比べ、消費電力や回路サイズが大きくなるFPGAは、演算性能をさほど求められないDSPアプリケーションには適さないと見られてきた。

その既成概念を変えそうなのが、アルテラの28nmFPGA製品が採用する「可変精度DSPブロック」である。その名の通り、乗算器の精度(入力データのオペランド幅)を変えられるのが特徴である。ローエンド「Cyclone® V」からミッドレンジ「Arria® V」、ハイエンド「Stratix® V」まで、アルテラFPGAの3ファミリに共通するDSPアーキテクチャだ。

乗算器精度を選べる可変精度DSPブロック

最近のFPGAは、大規模なDSP向け回路ブロックをハードウェアIPとして標準装備する。その演算性能は、搭載可能な乗算器の個数と動作周波数で決まるが、プロセス微細化により数千個の乗算器が数百MHzで稼働し、最大演算性能が1テラMAC/sを超えるFPGAも登場している。ただし、乗算器の精度は18×18ビット、18×25ビットなどで固定されてきた。

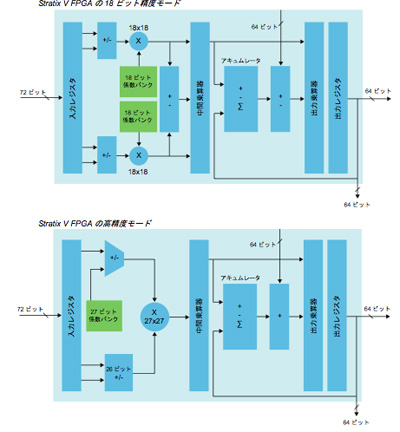

これに対してアルテラFPGAの可変精度DSPブロックは、9ビット・18ビット・27ビットの精度をネイティブサポートし、DSPブロックごと「18ビット精度モード」もしくは「高精度モード」を選べる。これが「可変」と称するゆえんだ(図1)。

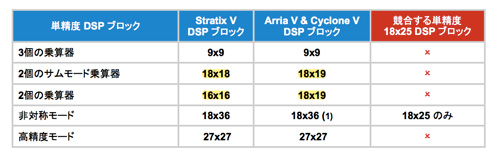

ハイエンドのStratix Vでいえば、各DSPブロックでコンフィギュレーション可能なのは、18ビット精度モードで3個の9×9(ビット)乗算器、2個の16×16/18×18乗算器だ。後者の場合、FIRフィルタなどで多用される、2個の乗算器の出力を加算(減算)する「加算モード」も使える。一方、高精度モードでは、1個の18×36乗算器か27×27乗算器である。

ミッドレンジのArria VとローエンドのCyclone VもStratix Vと同じく9×9乗算器から27×27乗算器までをサポートするが、大きな違いは18×18乗算器の代わりに18×19乗算器を用いること。18×19乗算器では、18+18ビットの前置加算器(プリアダー)から出力される 19ビット(追加された1ビットで正負の符号を表す)の結果をフルに受け入れ可能になる。(図2)。

必要なFPGAリソースは2分の1、3分の1

可変精度DSPブロックの最大のメリットは、ターゲット機器およびDSPアルゴリズムごとに乗算器の精度を変えられ、FPGAリソースを効率的に使えることだ。

ターゲット機器でいえば、例えば、監視カメラなら9×9ビット、放送機器なら16×16ビット、ワイヤレス機器なら18×18/18×25ビット、医療画像機器や軍事機器なら18×18/18×36/27×27ビットといった使い分けである。DSPアルゴリズムでいえば、低精度なビデオ・画像処理から高精度な浮動小数点FFTまで対応できる(浮動小数点機能については後述)。

こうした可変精度DSPブロックと、18×18ビットや18×25ビットで乗算器の精度が固定されたDSPブロックを比べれば、どちらがリソースを無駄なく使え、性能や消費電力の面で有利かは明らかだろう。

100個の9×9乗算器を必要とするケースで考えてみると、固定精度では精度が過剰な18×18ビット、18×25ビットの乗算器を1つずつ搭載したDSPブロックが100必要になる。それがアルテラFPGAなら各DSPブロックに9×9乗算器を3個ずつ埋め込めるため、必要なDSPブロックは34で済む。

また、18x36ビットという高い精度要求に対して、18×18乗算器や18x25乗算器なら2つのDSPブロックを接続する必要があるが、アルテラFPGAは1つのDSPブロックで実現する。

つまり、ほとんどの要求精度について、可変精度DSPブロックは固定精度に比べて3分の1、2分の1のリソースで対応できる。大規模なDSPを作り上げる場合、この差は大きい。

従ってDSPブロックの数だけでアルテラFPGAと他社製FPGAのスペックを比較すると評価を間違えることになる。一例を挙げると、Arria V(5AGXB3)のDSPブロックは1045なのに対し、同等クラスの競合製品は1440だが、ほとんどのケースで搭載できる乗算器の数はArria Vの方が多くなる。

64ビットバスで精度劣化のないカスケード接続

可変精度DSPブロックでは、DSPブロックのカスケード接続に64ビット幅の出力バスを用い、複数の乗算器をつなげるだけで27×27より高い精度の乗算器、複素数乗算器を実現できる。外部ロジックを使わないため、ここでも消費電力、回路サイズ、性能の面で有利だ。 例えば、18ビット精度モードのDSPブロックを2つカスケード接続すると、36ビットのフル分解能を持つ独立した18×18乗算器を3個搭載できる。また、高精度モードのDSPブロックを2つカスケード接続すれば36×36乗算器、4つ接続すれば、倍精度(64ビット)浮動小数点演算に使える54×54乗算器も実現可能である(54×54乗算器には外部ロジックが必要)。

また、複素数を扱う複素乗算器はFFTやDCTでよく使われるが、ここでも可変精度DSPブロックは有利だ。2つのDSPブロックをカスケード接続して18×18複素乗算器、3つ接続して18×25複素乗算器、4つ接続して18×36/27×27複素乗算器をそれぞれ実現できる。27×27複素乗算器の場合、単精度(32ビット)浮動小数点FFTに使えるだろう(図3)。

FPGAで容易に浮動小数点演算を実現する

可変精度DSPブロックは、固定小数点演算のみならず、高精度な浮動小数点演算にも容易に対応できる点が画期的である。 例えば、IEEE754が規定する浮動小数点演算の標準フォーマットは、32ビット単精度で仮数部は23ビット。これに符号と隠しビットのそれぞれ1ビットが加わる。この仮数乗算には、18x18乗算器なら4個、18x25乗算器なら2個が必要だが、27×27乗算器なら1個で済む。これは業界初である。このような浮動小数点演算を必要とするDSPアプリケーションは増えている――軍用機器では時空間適応レーダー、ワイヤレスシステムならMIMO(多入力・多出力)処理を伴うLTE チャネルカード、医療画像機器ではMRIやCT、計測器ではスペクトラム解析機など――こうした分野では浮動小数点FFTなどのDSPアルゴリズムが求められる。

アルテラの28nmFPGA製品で採用された可変精度DSPブロックは、「浮動小数点を取り扱うDSPアプリケーションにはFPGAは適さない」という既成概念を覆すもので、先端FPGAの柔軟性を示す特徴的な機能といえる。これまで消費電力や回路サイズの点からFPGAとDSPプロセッサの使い分けをしなければいけなかったケースでも、可変精度DSPブロックを活用することでFPGAリソースを効率的に使えるようになった。性能要件が高まるDSPアプリケーションにも、FPGAを積極的に活用できるようになったといえるだろう。

次回は浮動小数点に焦点をあて、浮動小数点DSPの概要と課題を説明し、FPGA上での実装フローについて紹介する。

(内容は変更される可能性があります。ご了承ください)。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

●Arria V&Cyclone V可変精度DSPブロックで実現する高性能信号処理

●高精度、高性能信号処理を実現する可変精度DSPアーキテクチャ

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。