第34回 こんなに使える!CPLD活用術(前編):FPGA Insights

「プログラム可能な論理回路デバイス」というと、FPGAを思い浮かべる読者が多いかもしれないが、他にもCPLD(Complex PLD)があることをご存じだろうか? CPLDもプログラマブル・ロジック・デバイス(PLD)の一種で、シリコンへの回路実装まで半導体メーカーが行うASICやASSPとは違い、技術者の手元で回路設計データを実装したり、修正したりすることが可能なデバイスである。設計途中での仕様変更や新しい規格にも柔軟に対応できること、また消費電力とコスト低減が進んだことで、最近ではデジタルカメラやスマートフォンにも採用されるようになっている。

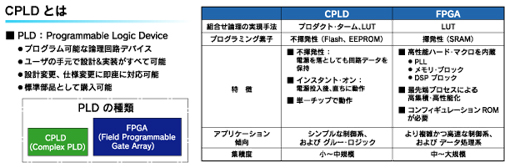

本稿ではまず、CPLDとFPGAの違いについて触れたい。両者は厳密に定義されているわけではなく、ベンダーによってもその解釈は若干異なるようだ。1つの見方として、プログラミング素子の違いを挙げることができる。CPLDの場合、フラッシュメモリやEEPROMのような不揮発性メモリを用いる。これに対してFPGAは、揮発性メモリであるSRAMが使われている。CPLDは不揮発性メモリを用いるため、電源を投入すればすぐに利用できるのが最大の特徴でもある。言い換えれば、ユーザーにとっては使いやすいデバイスである(図1)。

CPLDとFPGAの相違点を論理回路の規模で論じられることもある。CPLDは比較的小さい論理ゲート規模の領域をカバーしている。ざっくりといえば、CPLDでは1万ゲート以下の規模が一般的である。これに対して、FPGAでは、数万〜数100万規模に達する製品もある。

機能の複雑さでも違いはある。多くのCPLDでは複雑な機能を備えていない。例えば、乗算器やエンベデッドメモリなどは実装されていないことが多い。また、論理回路もCPLDは比較的シンプルな機能で、回路規模も小さい。その分、消費電力も小さくなる。

適用する製造プロセスでも、製品の特性にその違いは出てくるようだ。FPGAは一般的に最先端のプロセス技術を用いて製造される。これによって、機能や性能を追求しつつ、消費電力の低減などを図っている。一方、CPLDでは、その用途から見て必ずしも最先端プロセスで製造することが最適ではない。CPLDの場合、さまざまな電圧レベルの信号を取り扱い、その電圧レベルを変換するために用いられることがある。特に、産業機器においてはI/Oなどで5V系や3.3V系の電圧も多く使われている。これらの比較的高い電圧をサポートしていくには、高い耐圧を得ることができる旧世代のプロセス技術が必要となる。

組み合わせ論理手法で分けることもできる。CPLDでは、基本論理ブロックとなるのがマクロセルで、この内部はANDとORを組み合わせたアレイ構造(プロダクトターム)となっている。マクロセルの集合体がCPLDである。これに対して、FPGAはLUT(Look up table)方式が使われている。LUTはROMやRAMなどのメモリに、あらかじめ計算した値をテーブルとして書き込んでおき、書き込まれた値を必要に応じて参照する方式である。マクロセル方式に比べて、演算速度が高速で、チップ面積をより小さくできるというメリットがある。

プロダクトタームは、利点も多いが弱点もある。この問題も、組み合わせ論理手法を変えることで解決している。例えば、プロダクトターム構造のCPLDでは、マクロセル数が512を超えるとチップ面積が大きくなり、それがコストアップの要因となっている。この問題を解決するためにFPGAで使われているLUT方式を用いたCPLDも製品化されている。

アルテラのCPLD「MAX® V」や「MAX II 」がその一例である。MAX VやMAX II では、コンフィギュレーション用のプログラムを格納するフラッシュメモリをチップに内蔵しているため、電源を入れると瞬時にチップが立ち上がる。FPGAと同じLUT方式ながら、コンフィグレーション用メモリを外部に接続しているFPGAとはこの点が大きく異なる。回路設計者から見れば、MAX V やMAX II は瞬時にチップが立ち上がることから、従来のCPLDとほぼ同じ使い方ができる。

もう1つはプロダクトタームによる消費電力の問題である。当初のCPLDでは、スタティック電流を抑えることが、構造的に限界となっていた。そこで、スタティック電流の消費をできる限り抑えるために、回路構造をCMOSとした製品も開発された。こうすることで、待機時の消費電力を低減することはできたが、動作時の消費電力までは十分に下げることができなかった。

これに対して、アルテラの「MAX V」、「MAX II 」では、待機時だけでなく動作時にも消費電力を下げるための工夫を行っている。その1つが組み合わせ論理の実現方法を変えることであった。上述したように、MAX V / II はこれまでのCPLDで一般的に使われていたプロダクトターム構造ではなく、FPGAで用いられているLUT方式を適用している。その上、内部の電源系の回路も見直した。こうすることで、さらなる消費電力の低減を可能とした。この結果、MAXシリーズは、電池駆動のポータブル機器でも使われるようになった。最新のソフトウエアプラットフォームである「Android」OSを搭載した端末にもCPLDが搭載されるなど、設計者にとっては回路を実現する手段がこれまで以上に増えてきた。

さまざまな機能をCPLDで実現

CPLDとFPGAは互いに競合する製品ではなく、需要はともに拡大している。それは、同じプログラマブル・デバイスでありながら、使用する目的が異なるからである。アルテラのCPLDの場合、マクロセル数が128または256のMAXシリーズが出荷量では主力となっている。もちろん、マクロセル数が32/64といった製品群も依然として引き合いは多い。このような製品が使われるのは、電圧変換やI/O拡張といった用途である。

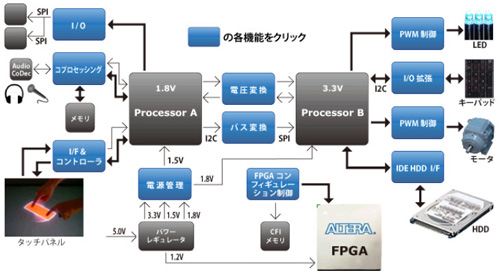

図2にCPLDで実現可能な機能を示す。その代表例が、次に挙げるような用途や機能である。

CPLDの需要が拡大している用途はいくつもあるが、まずその1つとして、「電源管理」を挙げることができる。1つのチップあるいはモジュールの中で、複数の電源系統が混載している場合、設計時に決められた順番と電源電圧で、回路ブロックを個別に立ちあげる必要がある。近年、論理回路の規模が大きくなって、電源リセットのシーケンスが複雑化していることもあり、その制御回路がCPLDに実装されるようになった。

電源管理は電話の交換機内部などでも行われている。かつての交換機だと、装置内部で使われる電源電圧は1〜2種類だった。最近ではチップ単体でも複数の電源電圧を供給しなければならず、その電源をオン/オフさせる順番も細かく決められている。その分、制御は難しくなる。複雑度が増せばますほど、CPLDにその機能を持たせた方が、制御回路をシンプルにすることができる。

CPLDの使われ方として多い用途をもう1つ挙げるとすれば、FPGAなどのプログラム制御がある。例えば、FPGAであれば電源を投入してコンフィギュレーションメモリから回路データを読み込むのが最もシンプルな使い方である。このハードシーケンスの部分をCPUによるソフトウエア処理ではなくCPLDで実行すれば、複数のFPGAに対して、必要なコンフィギュレーションを行うことができる。

さらに、MAX V 、MAX II に内蔵されたフラッシュメモリには、プログラム領域以外にデバイスIDやセキュリティ用の識別コードなどをユーザーが書き込むためのメモリ領域がある。この機能があることで、マイコン使用時に外付けしていたEEPROMなどが不要となり、回路基板上の部品点数を削減することができる。

後編では、さらにCPLDの使用方法について解説を続ける。

公開中(2011年2月〜2012年1月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

関連情報

●低コスト・低消費電力 CPLD による5 つの主要コントロール・パス・アプリケーションの実装

●ゼロ・パワー CPLD を使用したポータブル・アプリケーションにおけるトータル・システム・コストの削減

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。