基礎から学ぶシグナルインテグリティ:問題解決のためのポイントをつかむ(2/3 ページ)

電磁界解析ツールの活用

高精度のアナログ回路やRF回路の設計者らにとっては周知のことだが、信号には回路上のあらゆるものが影響を及ぼす可能性がある。シグナルインテグリティの対策では、何がシグナルインテグリティに影響を与えているのかを特定することから始めるべきであろう。

一般的な手法としては、設計している物の構成要素と配線に関するモデルを利用するシミュレーションが挙げられる。しかし、モデルというものは、現実に起こっている事象を十分に反映しているとは限らない。そのため、現実の回路を用いた各種の計測結果と、モデルを用いて行ったシミュレーションの結果を比較して、モデルを調整するという作業が必要になる。このようにして、より正確なモデルを得ることができれば、シグナルインテグリティを改善するための有効な手段をシミュレータによって検討できるようになる。シグナルインテグリティに影響を与える構成要素としては、IC内部のボンディングワイヤー、ICのパッケージ、プリント基板のビア、配線、コネクタなどが挙げられる。

モデルを用いたシミュレーションの目的は、設計した回路が実際にどのように動作するかを予測することである。マイクロ波やRF分野の技術者にとって、最新の電磁界解析ツール(例えば、Agilent Technologies社の「ADS(Advanced Design System)」など)を使用するのは当然のことだ。しかし、最近では、デジタル回路の動作周波数がマイクロ波の帯域に近づいていることもあって、デジタル回路のシグナルインテグリティの評価を行うために、デジタル分野の技術者も電磁界解析ツールを利用するようになってきた。こうしたツールを利用することで、反射や歪、クロストークといったシグナルインテグリティに影響を及ぼす要因についてシミュレーションを行うことが可能になる。また、電磁界解析ツールと、システムシミュレータや回路シミュレータを併用することで、より正確なシミュレーション結果を得ることができる。さらには、それらのツールを統合することができれば、個々のツール間のデータ転送などに要する時間を削減することも可能になる。

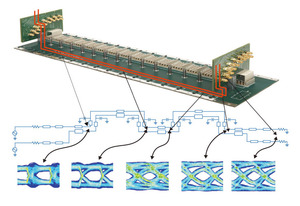

図3は、ドーターカードを挿入したバックプレーンに関するモデルを用いて、複数の個所のアイパターンを解析した結果である。このようにして、バックプレーンの配線やコネクタ、ドーターカードにおけるアイパターンを確認できる。これらのアイパターンから、どの個所でアイの劣化が起きるのか、そして設計のどの部分を変更する必要があるのかを見極めることが可能になるのだ。

正確なモデルを得ることができれば、設計した回路の動作をより深く理解できるようになる。これによって、シグナルインテグリティ以外の問題について、改善を図りやすくなることも大きなメリットと言えるだろう。

計測器による実測

上述したように、モデルの精度を向上するには、実際の回路の性能を測定した結果が必要になる。すなわち、計測器を用いた物理的な測定を行わなければならない。これらの物理的測定は、時間領域の計測器であるTDR(時間領域反射法:Time Domain Reflectometry)計測器や、周波数領域の計測器であるVNA(ベクトル信号アナライザ:Vector Network Analyzer)などを使用して行う。データ転送速度が高速である場合には、時間領域と周波数領域の両方で、測定データを解析することが重要になる。

配線についての測定に不慣れであるのなら、まずTDR計測器(Agilent社の「54754A」など)を使用することを考えるとよい。TDR計測器が表示する波形は直観的に理解しやすいので、最初に使用する計測器としては適切だと言える。

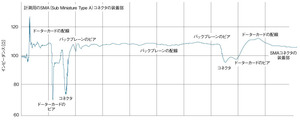

TDR計測器は、インピーダンスを測定して表示する。理想的なシグナルインテグリティが実現されている場合、インピーダンスの測定結果は平らな線になる。しかし、実際にはそのようになることはない。図4は、先に示したドーターカードを挿入したバックプレーンに対するTDR計測器の測定結果である。この例では、ドーターカードとバックプレーンの接合部で、インピーダンスが大きく変化していることがわかる。シグナルインテグリティを改善するためには、インピーダンスが大きく変化しないような設計に変更しなければならない。

物理的測定において、さらに高い精度や帯域幅が要求されるのであれば、Sパラメータ(散乱パラメータ)に関する知識を習得した上でVNA(Agilent社の「N5241A」など)を使用すればよい。

このほかに、時間領域と周波数領域の両方の測定に対応する計測器(Agilent社のPLTS[Physical-Layer Test System:物理層テストシステム]など)も利用できる。

Copyright © ITmedia, Inc. All Rights Reserved.