デューティ比の電圧制御が可能な発振回路:Design Ideas

本稿では、電圧コンパレータを使って、便利なクロック発生回路を構成する方法を紹介する。

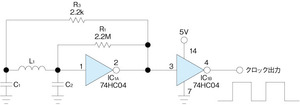

図1に示すのは、古典的なコルピッツ発振回路である。この回路では、インダクタL1、コンデンサC1、C2の値を変更することにより、発生するクロック信号の周波数を設定することができる。ただし、デューティ比を変更することはできない。

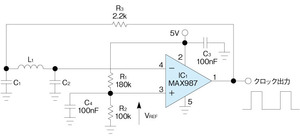

実は、この回路で使われているCMOSインバータIC1Aを電圧コンパレータで置き換えることで、もっと便利なクロック発生回路とすることができる。発振周波数だけでなく、デューティ比の設定も可能になるのだ。

図2に示したのが、その置き換えを行った発振回路である。図のとおり、コンパレータは、入出力の位相が180度シフトするよう反転構成で使用する。この位相シフトに、入力回路部(インダクタL1とコンデンサC1、C2で構成される部分)で生じる180度の位相シフトが加わることで発振が生じる。コンパレータでは、入力回路部からの正弦波電圧が基準電圧と比較され、出力がハイ/ローに変化することになる。

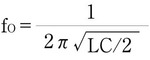

ここで、インダクタL1の値がLで、コンデンサC1、C2の値がいずれもCであるとしよう。そうすると、この回路の発振周波数fOは、入力回路部の定数L、Cを用い、次式で求めることができる。

実際の回路では、インダクタおよびコンデンサの値を適切に選択することにより、10MHz程度までの発振周波数を得ることができる。

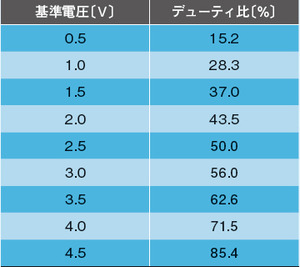

この発振回路のクロック出力のデューティ比は、基準電圧VREFの値によって決まる。その値は、抵抗R1とR2によって構成される分圧回路で簡単に設定できる。ただし、入力回路部から出力される正弦波電圧が線形ではないため、基準電圧の値とデューティ比の関係も非線形なものとなる(クロック出力の振幅も一定ではなく、デューティ比に依存する)。実際にどのような関係になるかは、例えばインダクタL1を10μH、コンデンサC1、C2を10nFといった値として評価を行うことで、簡単に把握することができる。

コンパレータとしては、ある程度高速であれば、どのようなものでもよい。例えば、米Maxim Integrated Products社の「MAX987」のように、入出力がレールツーレールタイプのものを使用すれば、基準電圧を広い範囲で設定できるようになる。その結果、デューティ比も広い範囲で設定可能になる。ただし、デューティ比の最小値を0%、最大値を100%にすることができないのは明らかであろう。

なお、コンパレータの伝搬遅延時間tPDによって、2πfOtPDに相当する余分な位相シフトが生じる。この位相シフトが入力回路部に影響を及ぼし、発振周波数は先述した式で求まる値よりもわずかに低くなる。また、基準電圧のレベルは、回路の保護の観点から、0.5V〜4.5Vの範囲で設定するのが望ましい。この場合、デューティ比は、ほぼ15〜85%の範囲となる(表1)。

Copyright © ITmedia, Inc. All Rights Reserved.