モバイル機器の進化はメモリインタフェースとともに:スマートフォンとタブレット端末がけん引(1/2 ページ)

スマートフォンとタブレット端末に代表されるモバイル機器は、市場が急激に拡大するととともに、PC並みの高い性能も要求されるようになっている。このため、モバイル機器向けメモリインタフェースの新たな規格を策定する動きが活発化している。本稿では、プロセッサの動作に不可欠なメインメモリとなるDRAMのインタフェースと、アプリケーションやデータを格納するのに用いるNANDフラッシュのインタフェース、それぞれの規格策定の最新動向を紹介する。

多くの選択肢が存在

携帯電話機やスマートフォン、タブレット端末をはじめとするモバイル機器の市場が急激に拡大するにつれて、モバイル機器向けの高性能かつ安価なメモリの需要も急速に伸びている。現在、モバイル機器に用いるメモリインタフェースには、メインメモリとなるDRAMとストレージとして使用されるNANDフラッシュメモリ(以下、NANDフラッシュ)の双方で多くの選択肢が存在している。数多くの業界標準が利用されている上に、今もなお新たに規格が策定されているのだ。この、誰もが急拡大していることを認める市場に用いられるメモリ技術やそのフォームファクタは一体どういったところに落ち着くのだろうか? 果たして、モバイル機器向けメモリの将来像とはどのようなものになるのだろうか?

eMMCとUFSを脅かすSSD

IHS iSuppliの予測によると、2011年のモバイル機器向けメモリの売上高は、前年比26%増の164億米ドルに増加する見込みだ。スマートフォンとタブレット端末の売れ行きの上昇に伴って、2012年には193億米ドルまで伸びると予測されている。Forward Insightsの主任アナリストであるGregory Wong氏も、民生用機器、特にスマートフォンとタブレット端末がメモリの需要を押し上げていることを認める。

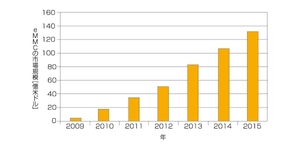

Wong氏は、「現在、これらの機器に利用されているストレージ用メモリのインタフェースは、大きく2つに分けることができる」と説明する。1つは、eMMC(Embedded Multimedia Card)である。eMMCは、JEDEC(Joint Electron Device Engineering Council:電子デバイス技術評議会)のSolid State Technology Association(半導体技術協会)が策定した規格で、低消費電力を特徴としている。図1に示すように、eMMCの市場規模は、スマートフォンやタブレット端末の市場拡大と同期するように増加を続けている。

もう1つのSSD(Solid State Drive)は、スマートフォンよりもさらに多くの記憶容量が必要なタブレット端末に用いられている。SATA(Serial Advanced Technology Attachment)インタフェースを備えるSSDは、JEDEC規格に準拠するeMMCよりも、IOPS(Input/Output Operations per Second)というデータ転送速度に関連するパラメータで優れている。その一方で、コストが高く、消費電力が大きいという欠点を持つ。

とはいえ、記憶容量を増加させながら、消費電力を小さくしつつ、性能も向上させることがメモリシステムの設計者にとっての最大の目標である。こうした目標の達成を約束する優れものとして多くの設計者に認識されているNANDフラッシュのインタフェースが、UFS(Universal Flash Storage)だ。ただしWong氏は、JEDECがUFSの初版の規格を発行した時に比べて、現在は関連メーカーによるUFSのサポート意欲が弱くなっていることから、「現在よりもSATAインタフェースの消費電力を低減できれば、SSDがUFSに取って替わる可能性もある」と見ている。「例えば、SATAは、PHY(物理層)の待機時消費電力が極めて大きい。しかし、待機時のPHYの動作をオフにすることができれば、消費電力を大幅に低減できるはず」(同氏)だという。

SanDiskは2011年5月に、タブレット端末を主な用途として意識した超小型パッケージの組み込み機器向けSSD「iSSD」を発表している(図2)。そして、SanDiskのみならず、全ての主要なメモリサプライヤがSSDを供給しているのだ。SanDiskの広報担当責任者を務めるMike Wong氏は、「ストレージ用メモリの真の課題は、消費者が望む価格で高性能かつ大容量の製品を提供することだ」と指摘する。さらに、Wong氏は、「新しいモバイル機器は日々市場に投入されている。しかし、ICや部品の共通化などによる開発体制の整備が果たされていなければ、インタフェースうんぬんの前に、機器の量産数量を確保することが優先的な課題になるだろう」と述べている。

LPDDR2とその後継規格

JEDECは、電子機器業界におけるオープンな規格策定に取り組んでいる。最近では、メモリ関連のテーマに焦点を合わせた標準化のミーティングをカナダのバンクーバーで主催した。半導体メモリ関連の委員会であるJC-42の議長を務めるDesi Rhoden氏は「JEDECの委員会で進行中のモバイル機器向けメモリを焦点とするインタフェース規格の策定結果は、業界に多大な戦略的影響を与えるとともに、革新的新製品を広範囲に生み出すように働くだろう」と話す。モバイル機器向けメモリに関係するJEDECの発行済み規格には、DRAMのインタフェース規格であるLPDDR2(Low-Power Double Data Rate 2)や、先に述べたNANDフラッシュのインタフェース規格であるeMMCやUFSなどが含まれる。

JEDECは、LPDDR2の規格仕様書であるJESD209-2Eの策定に当たり、スマートフォン、携帯電話機、PDA(Personal Digital Assistants)、GPS(全地球測位システム)ユニット、携帯ゲーム機などのモバイル機器の機能を向上できるように、メモリの高密度化/高性能化/小型化と、メモリシステム総体としての消費電力の低減を目標とした。この規格によって、先進的な電力管理機能、DRAMに代表される揮発性メモリとNANDフラッシュに代表される不揮発性メモリのI/Oの共有化、さまざまなレベルでのメモリ密度およびデータ転送速度を実現できるようになった。この規格は、低消費電力メモリを対象とするJC-42.6サブ委員会から2009年4月に初版が発行された後、2011年4月に改訂されている。

さらに、JEDECは、次世代のスマートフォンやタブレット端末が求める高性能化に対応するために、LPDDR2の後継規格であるLPDDR3を策定中だ。LPDDR3のデータ転送速度は、シングルチャネルで6.4ギガバイト/秒(GB/s)、デュアルチャネルで12.8GB/sまで拡大する。高速化の一方で、メモリチップをPoP(Package on Package)でプロセッサに組み込む場合と、ディスクリートのメモリパッケージを用いる場合の両方をサポートし、電力管理機能や信号伝送インタフェースのアーキテクチャはLPDDR2の規格を受け継ぐことになる。つまり、LPDDR3は、LPDDR2との互換性を維持するとともに高速化も目指す規格と言える。

これに対して、LPDDR3よりもさらなる高集積化、高速化、レイテンシ(遅延時間)と消費電力の低減、機器の軽量化/小型化が求められる際に、より革新的な技術を用いてメモリの高集積化や高性能化を果たす際の規格として策定されているのがWideIO(Wide Input Output)である。JEDECは、WideIOが、将来的なスマートフォン、タブレット端末、携帯ゲーム機などの高性能モバイル機器が要求する、性能、エネルギー効率、コンパクトさを提供できるとしている。なお、WideIOでは、TSV(Through Silicon Via:シリコン貫通電極)を用いたメモリチップの3次元積層技術を利用することになる。WideIOで実現できるデータ転送速度は、シングルチャネルで12.8GB/s以上と言われている。

Copyright © ITmedia, Inc. All Rights Reserved.