モバイル機器の進化はメモリインタフェースとともに:スマートフォンとタブレット端末がけん引(2/2 ページ)

eMMCの進化とUFSの策定

JEDECは、先述したeMMCとUFSの規格策定についても注力している。eMMCについては、2011年6月に、規格仕様書であるJESD84-B45のバージョン4.5を発行することを発表している。同規格は、低コストのストレージのインタフェースとして策定された。主な用途は、スマートフォン、カメラ、オーガナイザ(電子手帳)、PDA、ICレコーダ、MP3プレーヤ、ページャ(テキスト表示画面付きのポケベル)、電子玩具などである。eMMCの最新仕様では、データ転送速度が従来の104Mメガバイト/秒(MB/s)から200MB/sに高速化されており、消費電力の低減も実現されている。

UFSの規格仕様書であるJEDEC JESD220は、高性能と低消費電力が要求されるスマートフォンやタブレット端末といったモバイル機器向けのストレージを対象としている。同規格は、物理層として、MIPI(Mobile Industry Processor Interface)アライアンス(2003年7月結成)が策定した、M-PHYインタフェースを採用している。この先進的なインタフェースと、動作時消費電力の低減、そしてほぼゼロと言っていい待機時消費電力が組み合わされた結果、UFSは既存のフラッシュメモリ向けのインタフェース規格と比べて消費電力を大幅に低減できるようになった。JEDECは、この規格の初版を2011年2月に発行している。

互換性を重視するRambus

Rambusは、DRAMのインタフェースの開発と販売を行っているIP(Intellectual Property)企業である。同社の営業部門で上級マネージャを務めるKendra De Berti氏も、「やはり、スマートフォンとタブレット端末からのメモリに対する要求が多様な課題を生み出している」と語る。これらの課題の中には、動作時および待機時の低消費電力化、動作時から待機時、待機時から動作時への高速の電源切り替え、実装面積の低減、高速化、複数チャネルによるメモリ接続、処理能力の高いマルチコアプロセッサのサポートなどが含まれている。De Berti氏は、「今なすべきは、メモリインタフェースの基幹部分のアーキテクチャが上位互換性を有するようにすることだ。そうすれば、どのような仕様要求にも対応できる、低リスクのメモリを作り上げることができる」と指摘する。

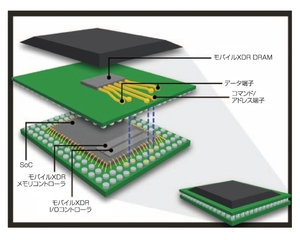

これらの課題に対処するため、Rambusが開発したのがモバイルXDR(Extreme Data Rate)アーキテクチャと、同アーキテクチャに関連するいくつかの技術である(図3)。例えば、同社の低振幅差動信号伝送技術を用いることで、低い動作電圧でも高速のデータ転送速度が可能になる。一方で、コマンド/アドレス信号がグラウンド規準のシングルエンド接続となっているLPDDR2やLPDDR3と互換性を持たせることのできる「FlexMode」と呼ぶ技術の開発にも多大な投資を行っている(関連ニュース)。

Rambusは、揮発メモリインタフェースの新規格であるWideIOへの対応にも積極的である。De Berti氏は、「TSV接続を利用するWideIOは、実装面積と消費電力を低減しながら高速化の実現も可能な技術だ。LPDDR2とLPDDR3の欠点を解決する可能性がある」と期待を込める。その一方で、同氏は、「WideIOを実現するために解決すべき課題は多い。TSV技術を適用したWideIOを、高い歩留まりかつ低コストで製造できるようになるまでには、多大な開発努力を要するだろう。さらに、プロセッサとメモリを1パッケージに統合した“ミックスドIC”が広く採用されるようになるためには、半導体のサプライチェーンとビジネスモデルに大幅な変革が必要になるだろう」と付け加えた。

デファクト化したNANDフラッシュ

モバイル機器の設計者は、NANDフラッシュのインタフェースを選択する際に、性能、フォームファクタ、電源融通性に関心を寄せる。東芝の米国法人であるToshiba America Electronic Components(TAEC)のメモリ事業部でバイスプレジデントを務めるScott Nelson氏は、「高い集積度と低コストという優位性により、NANDフラッシュがモバイル機器向け不揮発性メモリデバイスにおけるデファクトスタンダードとなっている」と主張する。同氏の見るところでは、モバイル機器の設計者はおおむね、raw NAND(NAND単体)、eMMC、SD(Secure Digital)カードやマイクロSDカードなど、インタフェースの差はあってもメモリデバイスそのものはNANDフラッシュを採用している。

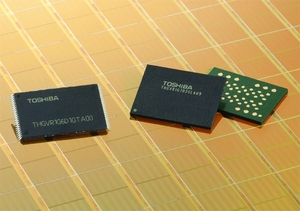

NANDフラッシュサプライヤにとっての大きな課題の1つが、次世代NANDフラッシュで対応すべき誤り訂正機能の改善である。そこで、東芝はECC(Error Correction Code:エラー訂正回路)を搭載するとともに、最先端プロセスで製造したフラッシュメモリを用いた「SmartNAND」を提案している(図4)。SmartNANDは、ECCコントローラチップとMLC (Multi Level Cell)タイプのNANDフラッシュモジュールを1パッケージ化したものである。

TAECのメモリ技術部門の責任者であるTetsuya Yamamoto氏は、「JEDECの策定する規格の進展に合わせて要求される高性能化に対応しなければならない」と考えている。例えば、eMMCの最新規格のデータ転送速度は200MB/sまで広げられた。一方、UFSのデータ転送速度は、eMMCの2倍弱となる3.0ギガビット/秒(375MB/s)にまで達している。東芝は、このような高性能化の要求に対応するため、「eMMCに加えてUFSもNANDフラッシュを用いたデバイスのインタフェースとしてサポートする計画」(Yamamoto氏)だという。

Copyright © ITmedia, Inc. All Rights Reserved.