プリント基板のパワーインテグリティ(後編):シミュレーションツールの活用で実現する(1/2 ページ)

「電源品質の確保」を意味するパワーインテグリティ。最先端のICを搭載するプリント基板で、このパワーインテグリティを実現することは容易ではない。本稿の後編では、高集積化が進むデジタルICに関連する電源品質の問題について簡単に説明してから、有力ベンダーが提供するパワーインテグリティ用シミュレーションツールの最新動向を紹介する。

デジタルICがDC問題の元凶に

FPGAやSoC(System on Chip)などのデジタルICは消費電流が比較的大きい。このため、電源供給において直流(DC)に関する問題を起こす可能性がある。また、これらのデジタルICは電源レールの本数も多いので、電源プレーンを複数用意しておく必要がある。さらに、端子数も数百本と多く、そこから引き出される配線のためプリント基板(PCB)に数百個のビアホールが設けられる。これらの銅パターンは、PCBの電源プレーン/グラウンドプレーン上で大きな面積を占める。こうしたPCBを設計する際には、各プレーンに形成する銅パターンの電流密度が十分に低く抑えられていることを保証しなければならない(図5)。

大きな値のDC電流は、熱に関する問題をもたらすこともある。例えば、銅の抵抗温度係数は0.4%/℃であり、これは温度が25℃上昇するごとに抵抗値が10%増えることを意味している。デジタルICに大きな処理負荷がかかるとその分温度が上昇するので抵抗値は増加する。抵抗値の増加は回路動作に対する信頼性の低下につながる。また温度上昇により、PCBに実装された部品の寿命が短くなってしまう。

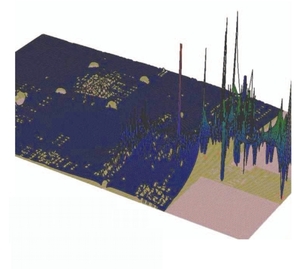

デジタルICにDC電流を供給するのに十分な面積の銅パターンを確保したら、今度は電源プレーンの交流(AC)に関する設計にも注目する必要がある(図6)。パワーインテグリティに関するシミュレーションを行うことにより、プレーン内のどこに帰還電流が流れるのかを検証できる。デジタルICが動作中に消費する電流の大きさは、ナノ秒の単位で大きく変動する。電源系はこの負荷電流の大きな変化、すなわちdi/dt(電流の時間微分)で表わされる電流変化速度によって、ICの端子上に大きな電源電圧の変動が生じることが無いようにインピーダンスを十分に低く抑えておかなければならない。またdi/dtは電磁放射とも関連するため、EMI対策を行う上でも重要になる。

結局のところ、PCBの回路設計で課題となっている、シグナルインテグリティ、パワーインテグリティ、EMI適合性は相互に関連している。さまざまな条件が複雑に絡み合っている以上、PCBの設計時にはシミュレーションツールを用いるべきだ。シミュレーションを行わずに設計したPCBでは、ビア間のクロストークをはじめとする数々のが発生し、どこから設計を修正して良いか収拾がつかなくなる可能性もある。

ソルバーによって異なる解析機能

RF(高周波)ICやRFシステムの設計者が電磁界シミュレーションを行う場合、3Dのフルウェーブソルバーを日常的に使用している。しかし、PCBのように比較的大きな解析対象に3Dのソルバーを適用してシミュレーションを行うと、解析結果を得るまでに長時間の計算を行う必要がでてくる。この問題に対して、パワーインテグリティツールのベンダーは、2Dと3Dのソルバーを組み合わせるハイブリッドの解析手法を導入することで計算時間の短縮を図っている。これらのツールの多くは、配線問題を解くために伝送線路理論を用いた高速テクニックによる2Dソルバーを使用している。また、平面に関する解析では、2Dまたは2.5Dの有限要素法を利用できる。ツールによっては、抵抗やコンデンサ、コイルなどの集中定数素子によってPCBのビアをモデル化することも可能である。ただし、より正確な解析結果を得るためには、ビアに対して3Dのフルウェーブソルバーを適用する必要がある。また、電源分配回路内に存在するコネクタ端子やその他の3Dの構造体によるパワーインテグリティへの影響を解析する場合にもフルウェーブソルバーが必要になる。

パワーインテグリティツールは熱解析の機能を搭載していることがある。熱解析機能を持つツールとしては、Mentor Graphicsの伝送線路解析ツール「HyperLynx」などが挙げられる。さらに、同社の熱流体解析ツール「FloTherm」に対して熱に関する情報をエクスポートすれば、システムや筺体(きょうたい)全体の熱的性能をモデル化することができる。

Agilent Technologiesは、電源プレーンとグラウンドプレーンに多くのビアを設けたPCBに関するシミュレーションをより正確に行うために、電磁界解析ツールの「ADS(Advanced Design System) Momentum」の機能強化を進めている。このツールのソルバーはモーメント法を採用しているので、マクスウェルの方程式の全要素を含む3Dの電磁界シミュレーションを高速で解析できる。PCBであれば、多層配線構造に関する電磁界シミュレーションをより高速に行えるわけだ。また、ファラデーの法則の高周波効果や、アンペール‐マクスウェルの法則で扱う変異電流を扱うこともできる。なお、大面積の2D平面に対して、モーメント法によるシミュレーションを行うと通常は長い時間が必要になる。そこでAgilentは、2D平面に関する解析について高速かつ正確な結果を得られるようなアルゴリズムを開発した。同社の高速デジタルプロダクト部門でプロダクト・マネージャを務めるColin Warwick氏は、「このアルゴリズムはツリー構造をベースにしており、モーメント法では実現できない直流の電磁界解析が可能だ」と語る。

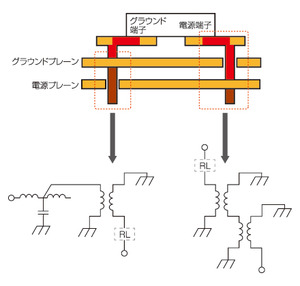

NEC情報システムズのパワーインテグリティ設計支援ツール「PIStream」のソルバーは、PCBの各プレーンについて集中定数素子の等価回路としてモデル化する部分要素等価回路(PEEC:Partial Element Equivalent Circuit)法を用いている。集中定数素子のマトリクスとなった各プレーンのモデルは、SPICEシミュレータや他の集中定数素子を用いた解析にも利用することができる。またこのツールは、グラウンド/電源プレーン間のエネルギー伝達についても、ビアの抵抗やインダクタンスを計算した上で集中定数素子モデルを生成する(図7)。さらに、キャパシタの寄生抵抗と寄生容量、ファンアウト配線、ヴィアの寄生抵抗と寄生インダクタンスを組み合わせた直列のRLC(抵抗/インダクタ/キャパシタ)回路を用いてデカップリングキャパシタのモデルも生成する。これらの集中定数素子モデルを用いることで、対象となるPCBのパワーインテグリティ解析を迅速に実行することができる。加えて、ツールの設定を変更することにより、PCBの全てのプレーンを考慮に入れた多層構造解析さえも可能になる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング