複雑なA/Dコンバータの回路構成を極める!:いまさら聞けないコンバータ入門(2)(2/3 ページ)

一般的な用途には最も使い勝手のよいコンバータですが、高精度が必要な場合は、その周辺素子の選び方に注意が必要です。

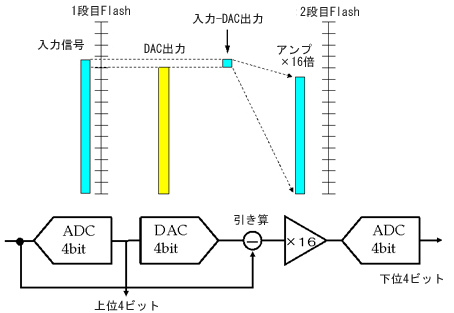

逐次比較型より速度が必要で、並列型より高分解能と精度が必要な場合、サブレンジング型A/Dコンバータが使用されます。このコンバータは、パイプライン型A/Dコンバータとも呼ばれます。内部は、低分解能(低ビット数)の並列型A/Dコンバータと同じビット数のD/Aコンバータを組み合わせたブロックを、アナログの引き算器とアンプを介して何段かつなげたものです。

図4は、2段だけの原理図ですが、実際に3段から5段くらいこのブロックが続き、分解能を稼いでいます。

図の2段構成では、初段の並列型A/Dコンバータで4ビット分の粗い変換を行い、その結果をD/A変換して信号から引き算をします。この差は、初段の1LSB以下の部分の信号になるので、これをアンプで16倍して次段のA/Dコンバータで変換をします。

ちょうど1段目と2段目でCourseとFineの変換を行ったことになり、理論的には2つの段の結果を足した8ビットが変換出力されます。実際には、これらのブロック間のつなぎがずれたりするので、デジタル回路による変換データの補正が必要になります。

この回路の良いところは、ビット数(分解能)が増えても並列型のようにコンパレータ数が膨大にならないことと、各ブロックは自分の変換が終われば全体の変換終了を待つ必要がなく、次の入力信号をすぐ処理できることです。

従って1ブロック分の処理時間で次々と高速・高分解能のAD変換が可能になります。12ビット〜16ビットの分解能で、数100MSPSの変換速度が実現されて、特に広ダイナミック・レンジと高分解能を必要とする通信システムや計測機器、医療機器などに使われています。

ただしデータは各ブロック間をバケツ・リレー式に送っていくので、何回かの変換クロック入力で最終結果が出てきます。変換クロックを何個か入れると、そのときの変換結果が出力され、その後はクロックのスピードでデータが出てきます。このクロックとのずれをパイプライン・ディレイ、あるいはレイテンシィと呼び、このタイプのコンバータの特長となっています。

ブロック間の信号バケツ・リレーにはサンプル・ホールド・アンプを用いますが、このバケツは完ぺきなものではなく、必ず漏れがあり、長い時間信号を入れていると内部の値が変わってしまいます。これをドループと呼びますが、この現象のためサブレンジング型A/Dコンバータには、変換動作の最高速度と併せて最低速度の制限もあるのが普通です。

並列型や逐次比較型のように、必要なときに変換クロック(変換スタートのコマンド)を送り、使わないときは動作を止めておくということが難しく、常に動いていないと正確な変換ができません。

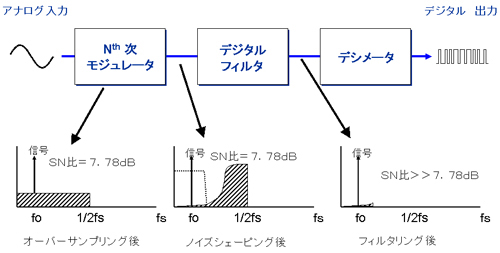

シグマ・デルタ型A/Dコンバータは、このD/Aコンバータの場合と同じように、オーバーサンプリングとノイズシェーピングという信号処理技術を駆使して構成されています。図5のように各ブロックでのスペクトラムはDAの場合とよく似ています。

もともと7.78dBしかない1ビット・コンバータの変換ノイズ(量子化ノイズ)を、オーバーサンプリングとノイズシェーピングにより偏在させ、これをフィルタリングにより大部分を取り去ることにより、SN比(精度)を向上させています。

図では高い周波数にノイズを偏らせています。必ずしも必要なことではなく、場合によっては信号が真ん中辺りにあり、ノイズを帯域両端に偏らせる場合もあります。この場合はバンドパス・フィルターによりノイズを取り除きます。

Copyright © ITmedia, Inc. All Rights Reserved.

図4 4ビット2段のサブレンジング型A/Dコンバータ

図4 4ビット2段のサブレンジング型A/Dコンバータ 図5 シグマ・デルタ型A/Dコンバータ

図5 シグマ・デルタ型A/Dコンバータ