FPGAにステートマシンを実装する、アーキテクチャと実装手法の選択が要諦:プログラマブルロジック FPGA(2/2 ページ)

状態変数の符号化方式

状態変数はフリップフロップ群の内部に格納される。このフリップフロップ群の内容は、クロックエッジごとに更新される。状態変数の値が変化しなくても、更新は実行される。

フリップフロップ群を利用してどのように状態変数の値を表現するかは、ステート数によって異なる。それから、合成ツールに指定する符号化方式によっても違ってくる。一般的な符号化方式は以下の3つである。

- バイナリ符号:伝統的なバイナリシーケンスに従って符号化する方式

- グレイ符号:状態変数の符号化にグレイ符号を利用する方式で、その点を除くとバイナリ符号と同じである

- ワンホット符号:1個の状態変数に1個のフリップフロップを割り当てる方式で、同時に高レベルになるフリップフロップは1個だけで、その他のフリップフロップはすべて低レベルになる

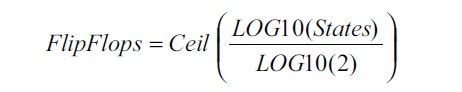

バイナリ符号方式とグレイ符号方式は、いずれも数多くのフリップフロップを必要とする。必要なフリップフロップの数は、次式で計算できる。

これに対し、ワンホット符号化で必要なフリップフロップの数は、ステート数と同じで済む。

開発では、ステート数の多少に応じて符号化方式を自動的に割り当てる。どの符号化方式を採用するかの境界は合成ツールによって異なるものの、一般的には次のような経験則を適用できる。

- バイナリ符号化:ステート数が5未満のとき

- ワンホット符号化:ステート数が5から50のとき

- グレイ符号化:ステート数が50を超えたとき

通常は、開発者がどの符号化方式を使用するかを検討する必要はない。合成エンジンにどの方式が適切なのかを判断させておき、選択した方式で問題が発生した場合にのみ、開発者が介入すれば良い。開発者が状態の符号化方式を定義し、ステートマシンの動作をきめ細かく制御する必要がある場合でも、状態の符号化に関して手作業で各状態の定数を定義する必要はない。次に示すように、コード内で属性を使用し、合成ツールに特定の符号化方式を選択させることができる。

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_encoding STRING;

ATTRIBUTE syn_encoding OF current_state : SIGNAL IS “sequential”;

ここで、「sequential」は「gray」または「onehot」に置き換えることができる。

また、これらの3つの選択肢(バイナリ、グレイ、ワンホット)を組み合わせることも可能である。それから、ステートマシンが無効な状態に移行したときに、safe属性を使用して有効な状態に復帰させることもできる。

さらに、syn_encoding属性を使って、ステートの符号の値を直接定義することも可能だ。例えば通常のシーケンスではIdle = “00”、led_on = “01”、led_off = “10”になるところを、下記のように記述すればIdle = “11”、led_on = “10”、led_off = “01”というスリーステートマシンを定義できる。

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_encoding STRING;

ATTRIBUTE syn_encoding OF current_state : TYPE IS "11 10 01";

開発者は、合成ツールが属性を無視しないように、合成ツール内で適切な設定値を使用させなければならない。例えばXilinxが提供するFPGA統合開発環境「ISE Design Suite」が備える合成ツール「XST (Xilinx Synthesis Technology)」では、“FSM Option”というオプション項目を“USER”に設定する。またSynopsysの合成ツール「Synplify」では、有限ステートマシンコンパイラ(FSM Compiler)をオフにしておく。

ここで、ステートマシンの実装に必要なフリップフロップの数を求める前出の式に戻ろう。ステートマシンの状態数は2のべき乗であるとは限らない。このため、可能な状態の一部は設計では使われないことになる。開発者は、これらの使われない「状態(ステート)」が適切に処理されるように設計しておく必要がある。無効な状態に移行したときは、正常に復帰できるようにしておく。

無効な状態から正常な状態に戻すには、2つの方法がある。1つは、合成ツールを利用して安全なステートマシンを実現することだ。合成ツールは、論理回路を追加することで、無効な状態を検出して有効な状態へと復帰させる、安全なステートマシンを実現する。もう1つの方法は、実装する論理回路をきめ細かく制御することだ。この方法では2のべき乗個の状態をすべて宣言し、別の属性を使って、エントリ条件を持たない状態でも削除されないような最適化処理を実行する。

ここで“エントリ条件を持たない”とは、シングルイベントアップセットといった一過性のエラーが発生したときを除き、いかなる条件によってもステートマシンが移行しない状態であることを意味する。このような使われない状態の削除を防ぐ属性の使用方法を次に示す。

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_keep BOOLEAN;

ATTRIBUTE syn_keep OF current_state : SIGNAL IS TRUE”;

結論に移ろう。安全で効率の高いステートマシンを設計することは、すべてのFPGA開発者が備えるべき技能である。ムーアマシンを選ぶか、ミーリーマシンを選ぶか、これらのハイブリッドを選ぶかは、システム全体の要件によって決まる。どのタイプのステートマシンを選択しても、実装に利用できるツールと利用方法を理解していれば、最適なソリューションを実現できるはずだ。

Profile

Adam Taylor氏

英国のEADS AstriumでPrincipal Hardware Engineerを務めている。FPGA開発の経験が長く、Xilinxの技術広報誌「Xcell Journal」をはじめとする業界各誌に、FPGAの活用方法に関する記事を数多く寄稿している。なおEADS Astriumは、欧州の大手航空・宇宙企業であるEADSの子会社であり、宇宙システム/サービスに注力する企業である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング