プログラマブル・ロジックを使ったVCO:Design Ideas アナログ機能回路

可変周波数の発振器を構成する方法として、NORゲートを2個用いたRC発振回路を考案した。この回路による可変周波数範囲は広い。

VCO(電圧制御発振器)はアナログ回路である。デジタル・プログラマブル・チップのライブラリーには含まれていない。信号の同期やクロックの逓倍でVCOが欲しいときには、ANDゲートやNANDゲートなどの標準論理機能を利用する必要がある。

可変周波数の発振器を構成する方法はいくつかある。例えば、バラクター・ダイオードを用いることによって周波数を変えられる。ただしこのダイオードは、電圧変化に対する周波数変化が小さい。従って、1個のインバーターと複数のコンデンサーで構成される一般的なピアース(Pierce)発振器では使いづらい。

別の案としてシュミット・トリガー・インバーターと、可変の充電抵抗を利用する方法がある。これは動作はするものの、ヒステリシスのばらつきが大きい。また、ICチップによって周波数が大きく変わってしまう。

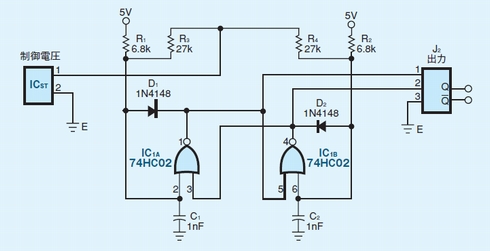

上記の理由から、NORゲートを2個用いたRC発振回路を考案した(図1)。この回路による可変周波数範囲は広い。

CMOSだけの回路だと、ハイレベルとローレベルのしきい電圧は約VCC/2になり、デバイスに依存しない。出力はデューティー比が50%の方形波になる。

電源投入時に図1のコンデンサーC1とC2は充電されておらず、NORゲートIC1Aの出力はローレベルである。するともう1つのNORゲートIC1Bの出力はハイレベルになり、コンデンサーC2は時定数R2C2で充電される。この充電時間には、ICSTから抵抗R4を経由してくる充電電流も影響する。

コンデンサーC2の電圧がVCC/2に達すると、IC1Bはローレベルに遷移する。するとIC1Aの出力はハイレベルとなり、C1は時定数R1C1で充電される。この充電時間には、ICSTから抵抗R3を経由してくる充電電流も影響する。一方でIC1Bがローレベルに遷移するとダイオードD2は順方向にバイアスされるので、C2が急速に放電される。

この回路は、C1=C2、R1=R2、R3=R4の条件で、50%のデューティー比を実現する。R4およびR3の値と制御電圧VSTが、VCOにおける周波数変化対電圧変化の利得(kHz/V)を決定する。

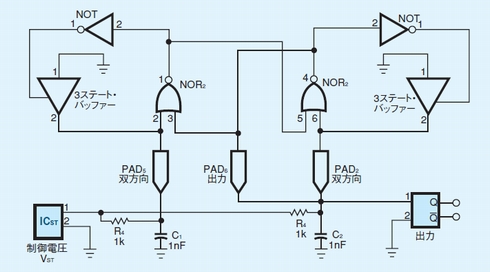

この利得を最大にする回路を図2に示す。ここでは米Altera社のPLD「EPM3032」を用いた。図1のダイオードを3ステート・バッファーに置き換えている。充電抵抗は制御電圧に直接、接続した。図2の回路定数を利用すると、約700kHz/Vという最も高い利得を実現できる。VCOを止めるときは、制御電圧をVCC/2よりも低くする。

CMOS入力を備えるPLDのほとんどで、この回路を構成できる。制御電圧は、電源電圧を超えても構わない。チップへの入力電圧はVCC/2を超えないからだ。このため、広い入力電圧範囲を有する電圧周波数変換回路に適している。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

関連記事

ジッタと位相ノイズの測定にPLLの分周器を活用

ジッタと位相ノイズの測定にPLLの分周器を活用

通信チャネルのデータ伝送速度が向上し、クロック信号の速度が高まるにつれて、ジッタと位相ノイズを高い精度で測定することがますます重要になっている。一方、測定の難易度は増すばかりで、高いコストが掛ってしまう。そこで本稿では、PLL ICの分周機能を活用して、測定器の性能限界を高める手法を紹介する。 大衆車にもミリ波レーダー衝突防止を――フリースケールがADAS新製品

大衆車にもミリ波レーダー衝突防止を――フリースケールがADAS新製品

フリースケール・セミコンダクタ・ジャパンがADAS(先進運転支援システム)対応のレーダーアプリケーション向け新製品を発表。高コストだった77GHz帯ミリ波レーダーのADASソリューションを、集積度を高めることで低コスト化。 衛星通信向けマイクロ波帯VCO、位相雑音は100kHzオフセットで−116dBc/Hz

衛星通信向けマイクロ波帯VCO、位相雑音は100kHzオフセットで−116dBc/Hz

ポイントツーポイント通信、計測/試験装置、衛星通信に向けたマイクロ波帯の電圧制御発振器(VCO)である。6品種あり、シリーズ全体で3.5〜13.9GHzの出力周波数範囲をカバーする。

Copyright © ITmedia, Inc. All Rights Reserved.