漏れインダクタンスを使用したフライバックコンバーター(1)ハードウェア概要:電源設計(2/5 ページ)

具体例として、以下の値を想定します。

Ileak=12μH Lp=600μH Ip1A Clump=150pF

Vout19V Vf=1V N=0.25Vin=330V Vclp=110V

この場合、式(11)にこれらの値を代入すると、電流は約976mAとなり、スイッチが開いた時点の元のピーク電流1Aに比べて2.4%減少していることになります。Clumpは非常に非線形的な項であり、またスイッチが開いた時点の低電圧では特にその傾向が強いことに注意してください。式(11)が理論に基づく近似式であることを踏まえ、ベンチを使用した実験を行いました。その結果、ダイオードDclpが導通を開始した時点でクランプネットワークを循環する電流は、これより小さい値であることを確認しました。(オフラインアプリケーションを想定した1kV定格の回路で)100pFのコンデンサーを追加してドレイン側の静電容量を大きくすると、この電流はさらに減少します。この追加コンデンサーは、ドレイン電圧のスナバとして機能し、RCDクランプ温度を抑える他、ターンオフ損失の点でも利点をもたらします。また、このノードでdV/dtを低減することによってEMIも改善されます。ただし、動作周波数が高い場合にこのコンデンサーを追加すると、高ライン電圧時のターンオン損失バジェットにとって妨げとなる可能性が生じます。この状況に対処するためのトレードオフを見つける必要があります。

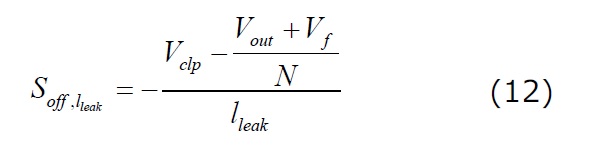

この時点で、(リップルを無視すると)漏れインダクタンス電圧は固定され、(クランプ・ダイオードによる降下を無視すると)低電圧側の端子はVin+Vclpの電圧にとどまります。このとき、高電圧側の端子はVin+(Vout+Vf)/Nに等しい電圧になっています。従って、漏れインダクタンスの両端に印加される電圧は、Vclp−(Vout+Vf)/Nになります。この時点で、漏れインダクタンスのリセット時間が開始されます。式(12)で定義された電流は、次式に等しい勾配で低下します。

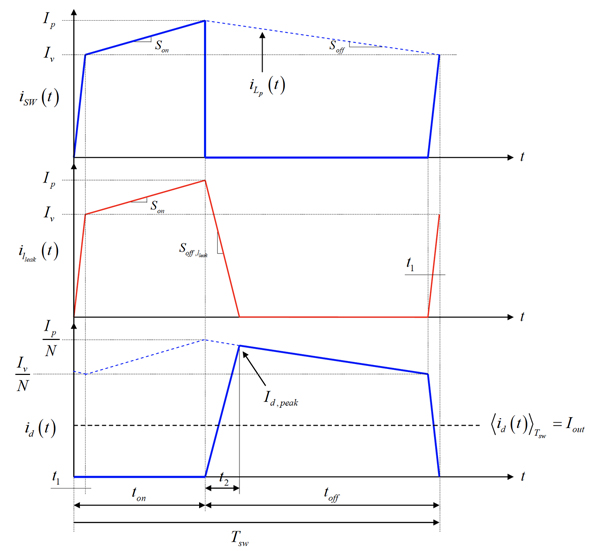

漏れインダクタンスがリセットされるので、2次側ダイオードを流れる電流id(t)は式(12)で定義された勾配に従って増加しますが、今回は正の方向であり、巻線比に従ってスケール化されます。漏れインダクタンスが完全に消滅した時点で、出力ダイオードの電流はピークに達します(図2b)。この時点で、2番目の電流は、(5)で定義された勾配で減少します。この下向き勾配はスイッチが再びオンになるまで持続します。この期間はオフ時間であり、記号toffで表されます。ただし、出力ダイオードの電流は瞬時にゼロに復帰することはできません。その理由は、漏れインダクタンスにエネルギーを蓄積するのに必要な時間です。漏れインダクタンスの電流は、1次側インダクタンスが2次側インダクタンスに結合している時の電流にまで大きく変化する必要があります。これは、スイッチ電流がゼロから増加して谷電流Ivに達するまでの時間です。ISW=Ivになると、全ての1次側電流が電力スイッチに流れ込み、2次側ダイオードはブロックされます。これらの情報から2つの重要な見解を導くことができます。

【1】2次側ダイオードは期間t1にわたって導通状態を維持します。t1が経過するとスイッチがオンになります。t1は漏れ電流が0から増加して谷電流Ivに達するまでの時間です。出力ダイオードはこの短期間にわたって導通したままなので、Lpは消磁状態を維持します。漏れインダクタンスはd1TSWだけ2次側ダイオードの導通時間を延長します。スイッチが閉じたにもかかわらず、漏れインダクタンスを流れる電流が谷電流に達して全体の流れがグランドに反転するまでは、1次側インダクタンスで勾配の変化は生じません。デューティ比Dはd1の割合で減少します。

【2】スイッチSWが開くと、Clumpを充電する漏れインダクタンスによって1次側電流全体が反転するので、2次側回路における2次側ダイオードの正味電流は0です。漏れインダクタンスがリセットされると、2次側電流が増加し、リセットが完了した時点でピークに達します。漏れインダクタンスは期間t2だけ2次側電流の発生が遅延し、ピークに影響を及ぼします。漏れインダクタンス内に蓄積されているエネルギーに加えて、1次側インダクタンスから奪われたエネルギーが、クランプネットワークで消費されます。

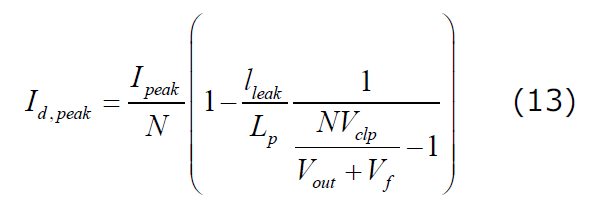

このイベントの詳細を図3に示します。図3を見て分かるように、漏れインダクタンスによる遅延の影響は明白であり、2次側電流が直ちにピークに達することを妨げています。さらに、このピーク電流はIpeak/Nではなく、[1]に示すように次式に等しくなります。

Copyright © ITmedia, Inc. All Rights Reserved.