1チップで実現した疑似ランダム雑音発生源:Design Ideas 信号源とパルス処理

米Microchip Technologyの1チップマイコン「12C508」を使って疑似ランダム雑音シーケンスを発生させる方法がある。今回の記事では、ループ当たりの必要マシンサイクルを最小限に抑えられるアプローチを説明する。

1チップで雑音発生源を実現

1チップの雑音発生源を探そうとすると、よくイライラする。以前は米National Semiconductorが、オーディオ機器向けに雑音発生源ICを製造していた。しかし今では、見つけることが難しい。このような状況にあるため、設計者はいくつかの選択肢の中から1つを選ばなければならない。しかし多くの手法は、複数のICが必要だ。例えば、ダイオードのアバランシェ雑音を大きな利得で増幅するアナログ方式や、多数のCMOS ICを使って線形帰還シフトレジスター方式の疑似ランダム雑音発生源を設計する方法などがある。

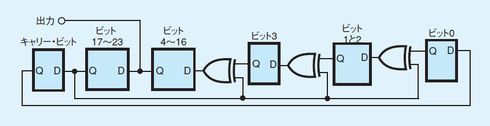

米Microchip Technologyの1チップマイコン「12C508」を使っても、雑音発生源を実現できる。この古典的な手法では、線形帰還レジスターをソフトウェアでモデル化し、疑似ランダム雑音シーケンスを発生させる。すなわち、多数のビットをテストし、XORをとって、単一ビットだけをシフトレジスターにフィードバックする。この方法には、実現可能な最大のビットレートは得られないという問題がある。そこで今回は、ループ当たりの必要マシンサイクルを最小限に抑えられるアプローチを示す(図1)。

今回の手法は、CRC(cyclic redundancycheck)のビットシフトアルゴリズムで用いているものと似ている。XOR演算は多数のビットについて並列に実行する。マイコンならば、並列演算は素早く行える。ビットテストとXOR演算は3命令サイクルで完了する。リスト1にアセンブラコードを示す。全てのループ処理で、わずか10命令サイクルしかかからない。

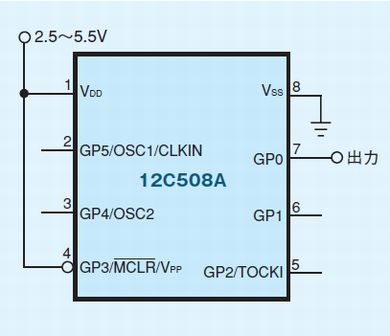

図2は、4MHzの発振器を内蔵した12C508で、100kHzの出力レートを得る回路である。シフトレジスターの実効的な長さは25ビットで、3バイトのデータと1つのキャリービットから構成されている。このような構成ならば、5分35秒までパターンの繰り返しは生じない。このほか出力レートを高める工夫として、8ビットの出力ポートを備えるマイコンを使い、そのポートをハイバイト(Hibyte)レジスターの代わりに用いる手法がある。この手法を採用した場合は、リスト1に出てくる命令である「movf Hibyte,W」ならびに「movwfGPIO」は不要になる。この結果、ループ処理は8命令サイクルで完了することになり、出力レートは25%増加する。なおI/O端子は、全て出力端子として設定する。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルター回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバー】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事から200本を厳選し、5つのカテゴリーに分けて収録した。

関連記事

ランダムなビット列を生成する回路

ランダムなビット列を生成する回路

従来のビット列発生器は、帰還をかけたシフト・レジスターを使って疑似ランダム・ビット列(PRBS)を得ていたため、有限長で同じパターンを繰り返すという問題を抱えていた。今回はこうした問題を打破できる、ランダム雑音を使って出力データ列を発生する回路を紹介する。 バスを5V 信号から保護する回路

バスを5V 信号から保護する回路

電圧を自動的に検出して、3.3V対応のPCIなどのバスを5V振幅の信号から保護する回路を紹介する。保護ダイオードや終端抵抗を用いて適切な終端電圧を設定すれば、1バス・サイクル以内でバスの信号振幅をある値に設定する回路としても使える。 パワーMOSFETを直流電子負荷に活用する

パワーMOSFETを直流電子負荷に活用する

太陽電池アレイやバッテリーなどの電源の試験に、電子回路によって構成した直流負荷を用いるが、市販製品は高価なものが多い。パワーMOSFETをリニア領域で用いると、電子負荷を自作できる。 高速クロックの逓倍回路

高速クロックの逓倍回路

理論上では、同期クロックの逓倍(ていばい)は簡単だ。しかし、周波数が高いクロックを逓倍する場合には高い周波数に対応したVCOを入手しなければいけない問題が生じる。今回はその問題を解決する回路を提案する。 PCのスピーカー回路でタイミングを制御

PCのスピーカー回路でタイミングを制御

PCでタイミングを制御する最も容易な方法は、遅延ループを利用することだ。今回は、PCのスピーカー回路を利用して、安定した遅延ループを得る方法を紹介する。 低速ADCを用いたサンプリングピーク検出器

低速ADCを用いたサンプリングピーク検出器

高速でサンプリングした信号のピーク値を、低速のA-Dコンバーターで測定できる回路を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:シフトレジスターの構成

図1:シフトレジスターの構成 図2:1チップマイコンを使った雑音発生源

図2:1チップマイコンを使った雑音発生源