リニアレギュレーターで電力を安定化するには:DC-DCコンバーター活用講座(1) 電力安定化(1)(3/3 ページ)

LDOレギュレーター

標準的なリニアレギュレーターで使用されるバイポーラパストランジスタは、電流アンプとして使用されます。エラーアンプの出力からの駆動電流にトランジスタの小信号電流利得(HFE)を乗じて、負荷電流を供給します。パワートランジスタのHFEは非常に小さい(標準20〜50)ので、複数のトランジスタによるダーリントン構成を使用して実効電流利得を高め、エラーアンプから流れ込む出力電流を低減します。

ダーリントントランジスタの短所は、各段のVBEによりドロップアウト電圧が上昇することです。PNPトランジスタを使ってNPNダーリントンを駆動する標準的なリニアレギュレーターにおける代表的なドロップアウト電圧は次のようになります。

周辺温度が低いとHFEが低下するため、全ての動作条件で信頼性の高いレギュレーションを得るには2.5V〜3Vのヘッドルームが必要な場合があります。

低ドロップアウト(LDO)リニアレギュレーターは、バイポーラトランジスタをPチャンネルFETで置き換えることにより、わずか数百ミリボルトのドロップアウト電圧で動作することができます。このとき、ドロップアウト電圧は抵抗RDSに負荷電流ILOADを乗じた、FETの順方向電圧に単純に一致します。一般に、RDSは非常に小さいので、ドロップアウト電圧も小さくなります。

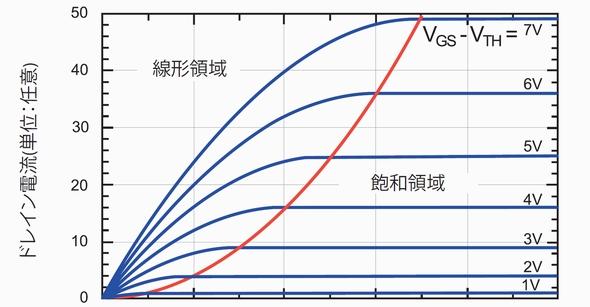

電流利得は温度と負荷の両方に依存する複雑な関係性を持つので、FETが抵抗性領域で使用されることはまれです(図4参照)。ただし、エラーアンプがVGS-VTH曲線におけるドリフトと非直線性を補償します。これは、エラーアンプがまさに出力電圧とレファレンス電圧を比較し、それに従って出力を調整するからです。

LDOの短所は、VGS-VTH曲線が、ゲート駆動電圧が高いとかなり急勾配になり、ゲート駆動電圧が低いと極めてへいたんになるため、エラーアンプが出力ジッタを非常に小さく(大きく抑制)しながら、同時に負荷や入力電圧の過渡に素早く応答する(わずかな抑制)必要があることです。その結果、高誘導性負荷または高容量性負荷という問題を生じ得る両極端な動作の間で、調整を図ることが求められます。

低ドロップアウト(LDO)リニアレギュレーターは、過電圧による損傷を非常に受けやすい場合があるので、フィルタリングを強化して過渡を抑制する必要があります。入力電圧範囲も、より制限します。

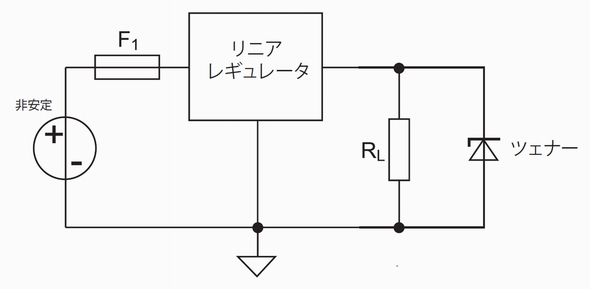

パストランジスタは大きなストレスを受けるので、標準リニアレギュレーター、LDOリニアレギュレーターともに内部の故障も生じやすくなります。パストランジスタの故障は通常、コレクタとエミッタの短絡です。つまり、制御なしに出力に入力が直接つながり、通常、アプリケーションは破損します。

図5に、パワーツェナークランピングダイオードを使ったフェイルセーフ保護回路を示します。レギュレーション障害が発生した場合、このダイオードによりヒューズが切断されます。

⇒「DC-DCコンバーター活用講座」連載バックナンバーはこちら

(次の記事を読む)

※本連載は、RECOMが発行した「DC/DC知識の本 ユーザーのための実用的ヒント」(2014年)を転載しています。

関連記事

リニアレギュレータの賢い使い方

リニアレギュレータの賢い使い方

煩わしいスパイクをなくすには、細心の注意と微妙な調整が必要である。 LDO型リニアレギュレータで実現する定電流源

LDO型リニアレギュレータで実現する定電流源

リニアレギュレータの電圧出力端子とグラウンド端子との間に固定抵抗を挿入すると、簡単に定電流源を構成できる。レギュレータの出力は定電圧であり、抵抗値が固定であれば、その両端を流れる電流は一定となる。今回は、負荷の高電位側にも低電位側にも定電流源を配置できる回路を紹介する。 レギュレータの電源投入時の突入電流制限回路

レギュレータの電源投入時の突入電流制限回路

電源サブシステム入門

電源サブシステム入門

リニアレギュレータ、スイッチングレギュレータなど、「電源」と呼ばれるものには多くの選択肢がある。本稿では、その選択肢のうちのいくつかの概要とそれぞれの問題点をまとめる。 電圧リファレンスICを正しく選ぶ

電圧リファレンスICを正しく選ぶ

電圧リファレンスICは、安定した固定電圧を必要とする電子回路を設計する上で必須のデバイスである。本稿では、まず、電圧リファレンスICの基本的な構成について概説する。その上で、ネオン放電管から最新のICに至るまで、電圧リファレンスに用いられる電子部品/ICの歴史をまとめる。さらに、電圧リファレンスICを選択するにあたって考慮すべき各種仕様について説明する。 負電圧電源をロジック信号でオン/オフする

負電圧電源をロジック信号でオン/オフする

今回は、ロジック信号によって負電圧電源を素早くオン/オフするときに役立つ回路を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.