LVDS PHY製品と伝送路の設計(その1):高速シリアル伝送技術講座(6)(4/5 ページ)

LVDSの伝送路設計(Part1)

LVDSの特長の1つは差動信号を使用し信号を伝送していることが挙げられます。そのため伝送路の設計では、基板伝送路やコネクター、ケーブルを介して差動信号の品質をなるべく落とさず受信デバイスまで伝達できるよう設計を行います。LVDSは0Hzから3Gbps程度までをサポートするI/Fです。デジタル信号は数百Mbpsから数Gbpsの帯域では伝送路の減衰特性、各部位のインピーダンスの暴れなどで、アナログ的な挙動となります。伝送路の設計では減衰や各部位のインピーダンス特性の管理が重要となるため、以下に基本的なLVDS伝送路の設計方法について説明をしていきます(より高速な差動伝送路の設計はCMLの応用編で説明していく予定です)。

基板の層数の選択とレイアウト

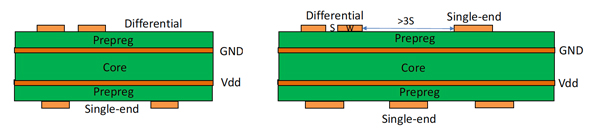

使用するプリント配線板(PCB)は最低4層以上を使用します。図15のように1層目はLVDSデバイスの実装と差動LVDS配線、2層目はリファレンスのGND、3層目は電源、4層目はシングルエンド信号に割り当て、シングルエンド信号ラインからのクロストークノイズを防ぎます。

6層以上で差動ラインを内層にレイアウトする場合でも同様に、差動ラインがシングルエンド信号ラインと結合してクロストークノイズを拾わないように、GNDや電源層を挟んで違う層へレイアウトし、分離します。

差動に限らず高速信号のマイクロストリップラインでは下層GNDと電磁気的に結合することで特性インピーダンスを有しています。そのため、高周波を扱う設計ではGND層と電源層は専用のべた層を割り当て、伝送路の特性インピーダンスが常に均一になるようにします。多層の場合はGND層と電源層の間隔を狭くすると低容量のバイパスコンデンサーと同様に高周波領域で優れた低インピーダンスの電源となります。

同層にLVDSとエッジレートの速いシングルエンド信号が混在する場合は、図16のようにLVDSの小振幅差動信号にシングルエンド信号からのクロストークノイズの重畳を避けるため、距離を離して配線します。内層への同層配線時も同様です。

以下に基本的なPCBレイアウトの順序を記載します。

- まず必要な各GNDと複数電源の層を割り当て、電源関係の層数を決定します。使用する各デバイスに対して、低インピーダンスのベタ層で電源が供給出来るよう、最優先でGND/電源層を割り振ります。

- 次にLVDSデバイスの配置位置と高速の差動伝送路の配線の概略を決定します。コネクターを使用する場合、LVDSデバイスはなるべくコネクター近くに配置し、ボード上のノイズをコネクターより先の信号配線へなるべく重畳させないようにします。コネクターとデバイスの距離が近いと差動配線長の差(イントラスキュー)を抑えることもできます。同層に差動信号とシングルエンド信号がレイアウトされる場合、クロストークを配慮し距離を離した設計ができるよう、余裕をもったレイアウトとしましょう。

- その他のデジタル部を設計します。デジタルデバイスは、LVDSデバイスのようなアナログデジタルミックスドシグナルデバイスに対してノイズ源となります。デバイスの配置は、配線同様に距離を離してレイアウトします。またデジタル電源からのノイズの回り込みが小さくなるように、アナログ電源はフィルターを使用してノイズ成分を減衰させたり、異なる層を割り当てたりします。

差動ラインの配線方法

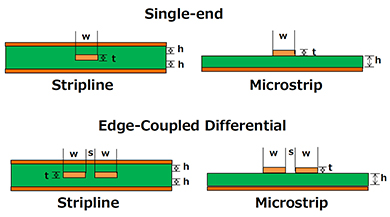

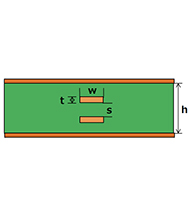

差動ラインは図17(下)のように表層に配線するマイクロストリップもしくは内層のストリップラインで配線を行います。これらをエッジ結合の差動配線と呼んでいます。図18の縦方向の差動配線(ブロードサイド結合)も可能ですが、層厚sはエッジ結合の配線のように細かく調整できないためエッジ結合のストリップやマイクロストリップラインよりも特性インピーダンスの調整が難しくなります。

GND層に挟まれた内層配線の差動ストリップライン構造は上下GND層によりシールドされるため、ノイズ放射の低減とノイズ耐性が大きく向上します。しかし上下のGND層との結合により、同じ配線幅(w)のマイクロストリップラインと比較し特性インピーダンスが低くなるので、注意しましょう。またストリップラインでは、デバイスとの信号接続は層間移動を行うためにビアを介した構造になり、ビア配線のスタブ(枝分かれした余分な伝送路)により高周波帯域に悪い影響を与えるため、ビアスタブがなるべく短くなる層を選択し配線します(ビルドアップやバックドリルなどでビアスタブがない構造の場合は問題ありません)。

Copyright © ITmedia, Inc. All Rights Reserved.

左=図15:高速差動信号、PCBレイアウト / 右=図16:同層へのレイアウト方法

左=図15:高速差動信号、PCBレイアウト / 右=図16:同層へのレイアウト方法

左=図17:ストリップラインとマイクロストリップライン。(上)シングルエンド (下)差動 / 右=図18:ブロードサイド結合

左=図17:ストリップラインとマイクロストリップライン。(上)シングルエンド (下)差動 / 右=図18:ブロードサイド結合