LVDS PHY製品と伝送路の設計(その1):高速シリアル伝送技術講座(6)(5/5 ページ)

差動配線の特性インピーダンスと計算

100Ωや90Ωなど、目標の差動特性インピーダンスが決まったら、PCBメーカーに対して特性インピーダンスを指定します。PCBメーカーは層間の厚さhと銅の厚さtが決まっている場合は線幅wと線間sを調節して指定の差動インピーダンスを決めています。その際、差動間の距離sが線幅wよりも小さい、電磁気的な差動結合が強い配線を指定しましょう。sが小さい差動配線では、差動の結合が強く自分自身で+と−の差動間スキューを吸収し、放射ノイズも低減します。sを小さくすることで希望の特性インピーダンスよりも低くなる場合は、層厚hの変更も検討しましょう。層厚hを大きくすることで、コモンモードインピーダンスを上げることができ、差動インピーダンス(Zdiff)をコントロールできます。

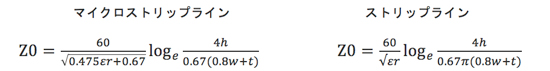

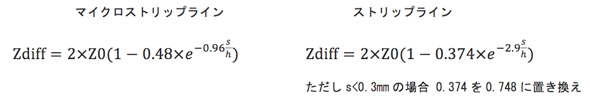

s、w、h、tの各寸法と比誘電率εrの値が分かると、エッジ結合の差動インピーダンスのおおよそを把握することができます。

下記式より、まずh、t、wの寸法から(a)のシングルエンドZ0を求め、次に(b)のsとhを使用しZdiffを求めます。

(a)シングルエンドZ0

(b)ディファレンシャル Zdiff

実際の測定値と計算値は通常、乖離(かいり)があります。基板メーカーは実測値から各パラメーターの特性インピーダンスに対しての影響を把握し、基板製造に適応させていますので、sの条件も含めて特性インピーダンスを指定しましょう。またインサーションロス特性(減衰特性)についても、誘電正接や表面粗さのパラメーターが追加されるため、調整を行わないと電磁界シミュレーションなどの結果と実際の測定値には乖離があります。

比誘電率(εr)と誘電正接(tanδ)

Z0の式には比誘電率εrが使用されていますが、表4のように使用する材質により比誘電率は異なるため、特性インピーダンスが変わります。

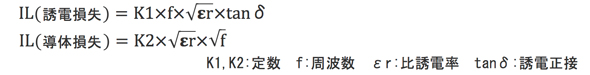

また誘電正接(tanδ)は、上記の特性インピーダンスを求める式では使用していませんが、伝送損失は式(c)の誘電損失と表皮効果などによる導体損失があり、誘電損失では周波数に対して掛け算の係数で使用されているように、ロスに対して大きく影響するため、誘電正接が大きい材質を使用した伝送路では単位長あたりのインサーションロスが大きくなります。

(c)伝送損失(インサーションロス)

| 誘電体(材質) | 比誘電率 εr | 誘電正接 tanδ |

|---|---|---|

| 空気 | 1 | 0 |

| テフロン | 2.1〜2.5 | 0.002〜0.0002 |

| ポリエチレン | 2.2〜2.4 | <0.0005 |

| ポリイミド | 2.8〜3.5 | 0.02〜0.004 |

| FR-4 ガラスエポキシ | 4.1〜5.3 | 0.02〜0.002 |

| メグトロン4 | 3.8 | 0.005 |

| メグトロン6 | 3.4〜3.7 | 0.002〜0.0015 |

今回はLVDS物理層製品とその使用方法、LVDS伝送路設計について説明しました。次回、連載第7回も引き続き伝送路設計とデバイス使用の際の注意点について説明していきます。

なお、本連載のテーマでもある「高速シリアル伝送設計」に関する技術セミナー(主催:ザインエレクトロニクス)を2018年1月31日に開催し、筆者も講師として登壇します。ご興味のある方は、下記Webサイトからお申し込みください。

【参考文献】

・ギガビット伝送システム開発力強化集中講座 CQエレクトロニクスセミナ2012 講演資料 河西基文.

・ナショナルセミコンダクタージャパン株式会社 LVDSオーナーズマニュアル 第3版/第4版

筆者Profile

河西基文(かわにし もとふみ)/ザインエレクトロニクス シニアエキスパート

ナショナルセミコンダクタージャパンやジェナムジャパンなど、25年にわたり高速通信系半導体の製品開発・サポートおよびマーケットの開拓に従事。伝送路を含んだ半導体の高速設計手法が確立されていない時代に、LVDSオーナーズマニュアルの作成など、同マーケットの成長・普及に寄与してきた。

現在は日本のSerDes製品開発の先駆者的存在のザインエレクトロニクスで、プロダクトマーケティング・開発支援や人材育成などを行っている。

関連記事

終端方式と高速シリアルI/Fデバイス

終端方式と高速シリアルI/Fデバイス

今回は、LVDS、CML/PECL、計測器などの終端方法と、シリアル伝送デバイスの種類について解説します。 接続形態(トポロジ)と特性インピーダンス

接続形態(トポロジ)と特性インピーダンス

今回は接続形態(トポロジ)、特性インピーダンスについてです。LVDS系テクノロジーのさまざまなトポロジとその基本な構成、またPECLやCMLを使用して同機能を高速で実現する方法などについて紹介します。 高速伝送の代表的な物理層 LVDS・PECL・CML

高速伝送の代表的な物理層 LVDS・PECL・CML

今回は、高速差動伝送で使用されている代表的な物理層である「LVDS」「PECL」「CML」の特長、接続方法、用途例を紹介していきます。 差動信号伝送のメリット ――使用されている技術と注意点

差動信号伝送のメリット ――使用されている技術と注意点

高速シリアル伝送技術について基礎から学ぶ本連載。2回目は、差動信号伝送の特徴、メリットに焦点を当て、使用されている技術や注意点について解説していきます。 PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

本連載では、さまざまな高速通信規格に使用されている物理層の仕組みや性能、SerDesの機能や特徴とその種類、高速伝送での主要なパラメーター、伝送路を含んだ技術や設計手法などを分かりやすく解説していく。 HDMI 2.0のできること

HDMI 2.0のできること

映像/音声の伝送規格として定着したHDMIの最新規格「HDMIバージョン2.0」(以下、HDMI 2.0)がこのほど策定された。ここでは、これまでのHDMI規格バージョンとHDMI 2.0ではどのような違いがあり、どんなことができるようになったのかみていく。

Copyright © ITmedia, Inc. All Rights Reserved.