入力電圧範囲の制限と同期整流:DC-DCコンバーター活用講座(10) 電力安定化(10)(2/2 ページ)

同期整流

既に述べたように、あらゆるコンバーターの効率低下の大きな原因の1つは、出力ダイオードによる電力消費です。パワーダイオードには標準で500mVの電圧降下が生じますが、これは1Aで0.5Wの電力損失に相当します。順方向電圧降下の小さいショットキー・ダイオードは、小電力コンバーターの代替として使用できる場合がありますが、大電流に対応できるサイズのものは高価です。しかし、それでも約200mVの順方向電圧降下があるので、電力損失は依然として顕著です。このような状況で効率改善を大きく前進させたのが、同期整流技術の開発です。

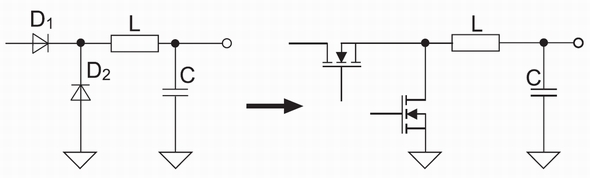

左側の図は、ダイオード整流による標準的回路です。この回路ではD1が整流器として、D2がフリーホイール・ダイオードとしての役割を果たします。どちらのダイオードにも、ほぼ同じ電流ILによる負荷が交互にかかります。ダイオード内での順方向電圧降下VFによる損失は、PVD=VFILです。標準順方向降下電圧VFを0.5Vとすると、相対的消費電力を1アンペアあたり0.5Wと仮定できます。よって、3.3V/10Aの出力コンバーターの電圧変換損失は15%です。これには、他のいかなる変換損失も考慮されていません。ダイオード内の消費電力は5Wなので、有効な動作温度範囲を設定するために、ダイオードにはヒートシンクを取り付ける必要があります。

幸い、サイクルの順方向部分でFETをスイッチオンし、サイクルの逆方向部分でスイッチオフすることにより、これを整流素子として使用することができます。FETは、抵抗RDS,ONが非常に低いという高速スイッチとしての利点を備えているので、整流器に最適です。これらのデバイスの欠点は能動的に駆動しなければならないことで、追加のタイミング回路や駆動回路が必要になります。これらの回路では、2つのFETを出力波形に同期させて正確にオン、オフするために、内部電圧を検出する必要があります。これがこのトポロジーの名前の由来です。これに対し、ダイオードは特別な回路を必要としない受動デバイスですが、約10mΩという非常に低いRDS,ONは、大出力電流コンバーター用にはより複雑な回路が必要になるという欠点を補って余りある利点です。一部の設計では、クリーンな駆動信号を生成するために、追加の2次側巻線が使われます。

通常、ダイオードはFETより逆降伏電圧の定格値が大きいので、既存のダイオード整流回路を設計して同期整流を使用する場合は、電圧過渡がVDSの制限値を超えないよう注意が必要です。

⇒「DC-DCコンバーター活用講座」連載バックナンバーはこちら

(次の記事を読む)

※本連載は、RECOMが発行した「DC/DC知識の本 ユーザーのための実用的ヒント」(2014年)を転載しています。

関連記事

スイッチノードリンギングの原因と対策

スイッチノードリンギングの原因と対策

昨今、広入力電圧範囲DC-DCコンバーターが使用されるケースが増えてきたが、MOSFETの高速のターンオンとターンオフは、スイッチノードのリンギングを発生させ、さまざまな障害の原因となっている。そこで、本稿では、DC-DCコンバーターにおけるスイッチノードリンギングおよびスパイクのメカニズムを取り上げ、その発生メカニズムと対策方法を詳しく解説する。 昇圧型レギュレーターに降圧動作を追加する

昇圧型レギュレーターに降圧動作を追加する

SEPICレギュレータには、変換効率や磁性部品の点で欠点がある。そこで、SEPICレギュレータの代わりとして使える回路を提案する。 電源の試験に用いる電圧制御型電流シンク回路

電源の試験に用いる電圧制御型電流シンク回路

同期整流器の動作タイミングを制御する回路

同期整流器の動作タイミングを制御する回路

同期整流器を採用する際に問題になるのは、スイッチングのタイミング制御が複雑になることだ。本稿では、この動作タイミングを制御する回路を紹介する。 ダイオードで学ぶパワーエレクトロニクスの基本

ダイオードで学ぶパワーエレクトロニクスの基本

半導体素子の基本を学びながら、パワーエレクトロニクスの核心に迫っていく本連載。今回は手始めとして、電気と半導体の基本を簡単に説明しつつ、半導体素子の基本であるダイオードを使った電力変換について解説していきましょう。 過電圧監視がない電源の末路

過電圧監視がない電源の末路

今回は、高価な電気メッキ装置用電源機器の修理エピソードを紹介する。故障原因は、しばしば見受けられる“配線切れ”だったが、事もあろうに過電圧監視が施されていなかったが故に、悲惨な末路を迎えてしまった。

Copyright © ITmedia, Inc. All Rights Reserved.