高速インタフェースで使用されるSerDes 〜 種類と特長、その歴史:高速シリアル伝送技術講座(9)(2/5 ページ)

2. クロックスピードを4倍にする

低速のバスクロック8MHzをバスデータとのACタイミングを満たし4倍の33MHzへの向上は可能でした。実際、PC-ATのISAバスはクロックスピード8.33MHz、その後発表されたPCIローカルバスでは33MHzを採用し、クロックは4倍のスピードとなりました。

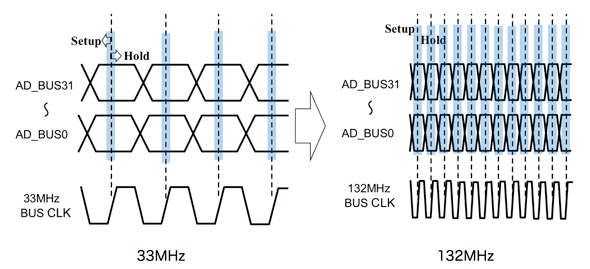

しかしこの33MHzのクロックスピードを4倍の132MHzとすると、受信側でのバス信号のデータとクロックのACタイミング要件(セットアップ・ホールド)を満たすことが困難になりました(図3)

またクロックスピードを上げることで、バスシステム本来の複数スロットのサポートが信号品質(Signal Integrity)悪化のために大幅に減少しました。1992年に発表された33MHzのPCI Local Bus Rev 1.0では4本のバススロットをサポートしていましたが、クロックを高速化したPCI-X Rev1.0規格(1999年)ではクロックスピードの上昇に伴い100MHzクロックでは2本、133MHzでは1本のスロットとなり、スロット数が大きく減少しました。

1980年代後半から1990年代にかけて、パラレルのバス信号構成のまま、バス幅の拡張とパラレルクロック周波数を上げる手法で8MHz/16ビットのISAバスから32ビットバス仕様のEISAバスや、32/64ビットバス・33/66MHzクロックのPCI、100/133MHzクロック仕様を追加したPCI-Xなどが策定されました。しかしながら、デバイスの指数的な処理能力の上昇に追いつくことはできませんでした。

またデバイスAとデバイスBの距離が離れている場合も、バスデータとクロックのACタイミング要件が破たんするため、データの正常な受信が不可能になります。

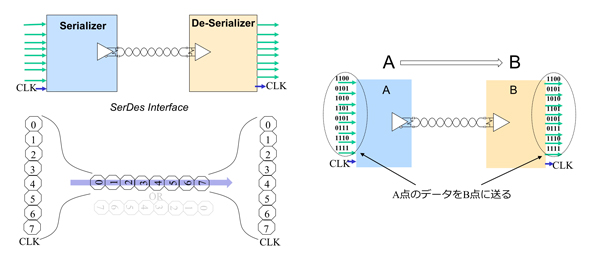

このパラレルバスの問題を解決する手法として、SerDesのアーキテクチャが採用されました。シリアライザ(Serializer)とデシリアライザ(De-serializer)をまとめて、SerDes(サーデス)と呼んでいます。この機能は図4左のようにシリアライザでパラレルのバス信号をシリアル化し、デシリアライザでこのシリアル信号のデータを元のパラレルバスの信号に戻す単純な仕様です。シリアライザAに入力したバスデータと同期クロックは図4右のようにデシリアライザBから同様に出力されます。

パラレルバス構造では伝送距離の延長や、クロック周波数を上げることが困難なため、距離のある伝送や高速伝送では、SerDesのシリアル化の機能を使用し、デバイスAからデバイスBへデータを伝送しています。

Copyright © ITmedia, Inc. All Rights Reserved.

図3:33MHz(左)、132MHz(右)バスクロックとパラレルデータのACタイミングマージン

図3:33MHz(左)、132MHz(右)バスクロックとパラレルデータのACタイミングマージン 図4:SerDesの機能

図4:SerDesの機能