高速インタフェースで使用されるSerDes 〜 種類と特長、その歴史:高速シリアル伝送技術講座(9)(4/5 ページ)

【2】01クロック埋め込み式SerDes

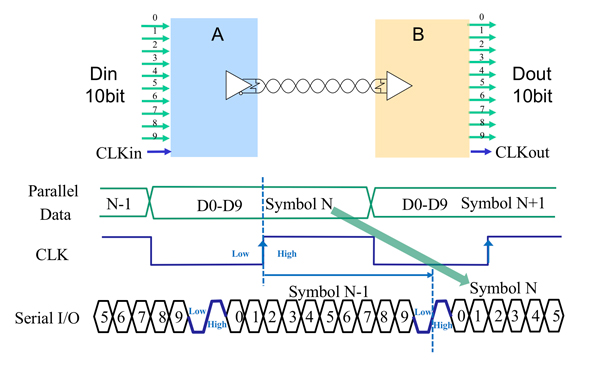

LVDS SerDesが発表された3年後の1998年、図9のパラレルバスのクロックLow(0)とHigh(1)をスタートとストップビットとしてシリアルデータに埋め込んだ、01

(ゼロイチ)クロック埋め込み式SerDesが発表されました。スタートストップクロック埋め込み式とも呼ばれています。

このデバイスはLVDS SerDesのアーキテクチャの流用で設計され、高速化や長距離化の際に課題であったLVDS SerDesのクロックとデータのスキューの問題を解決しました。

最初の製品は図9の10ビットのシリアルデータに0、1のクロック情報を埋め込んだ計12ビットのシリアル変換でしたが、その後データビットを増やし、18、20、21、26、31、66、67、130、132などのシリアルビット製品や規格が発売、発表されています。

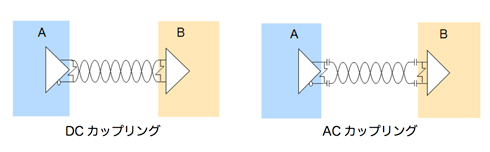

シリアライザ(TX)とデシリアライザ(RX)の距離が離れると個別の電源を使用するために、電源電位差(GND電位)への配慮が必要になります。この電位差の問題を解決するため、データラインにACカップリング(図10右)を使用しています。またTXとRXのGND電位が同じでも、CML I/Oでは送信と受信側の物理層がそれぞれ最適なコモンモード電圧で動作できるよう、同様にACカップリングが一般的に使用されています。

ACカップリングを行うとDCと低周波成分が伝送できないため、ACカップリングでSerDesを動作させる場合は、データストリームのDCバランスを保つためのスクランブル化やDCバランスビットの追加、シリアライザ側でDCバランスを保持させるための特殊パターンのパディングなど、規格や製品によりさまざまな対応を行っています。

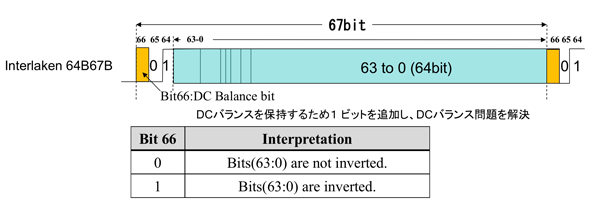

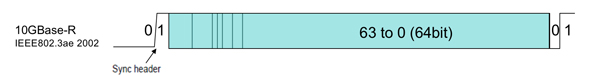

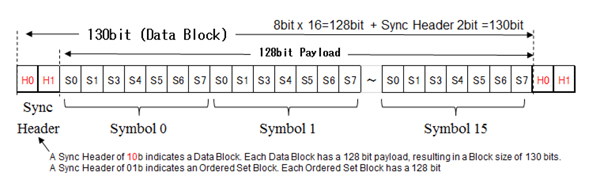

10Gbpsのイーサーネット規格IEEE802.3ae 10GBase-R 10GBase-Wで使用されている64B66B(図11-1)、そのデータ長を2倍にしたPCIe Gen3(8Gbps)の128B/130B(図11-2)、64B66BコーディングのDCバランスの弱点を解決したInterlaken 64B67B注1(図11-3)、PCIe Gen3で採用した128B130Bの信頼性向上を目指したUSB3.1 Gen2 SS+(10.3Gbps)の128B132Bも、このスタートストップクロック埋め込み方式に分類されます。

図11-3:Interlaken 64B67B コーディング(データワード送信時)

図11-3:Interlaken 64B67B コーディング(データワード送信時)注1:http://www.interlakenalliance.com/Interlaken_Protocol_Definition_v1.2.pdf参照

Copyright © ITmedia, Inc. All Rights Reserved.

図9:01クロック埋め込み式SerDes

図9:01クロック埋め込み式SerDes 図10:DCカップリング(左)とACカップリング(右)

図10:DCカップリング(左)とACカップリング(右) 図11-1:10GBASE-R 64B66Bコーディング シリアルストリーム(データワード送信時)

図11-1:10GBASE-R 64B66Bコーディング シリアルストリーム(データワード送信時) 図11-2:PCIe Gen3 128B130B コーディング

図11-2:PCIe Gen3 128B130B コーディング