高速インタフェースで使用されるSerDes 〜 種類と特長、その歴史:高速シリアル伝送技術講座(9)(3/5 ページ)

SerDesの種類と特長

SerDesを機能仕様から大きく分類すると、

【1】LVDS(EIA/TIA-644)物理層を使用したLVDS SerDes

【2】スタートストップビットを埋め込んだ01クロック埋め込み式SerDes

【3】8B10Bコーディング採用の8B10B SerDes

の3種類に分けることができます。以下にこれら3種類のSerDesの歴史とそれぞれの機能、特長について説明していきます。

【1】LVDS SerDes

LVDS物理層を使用したSerDesの始まり。

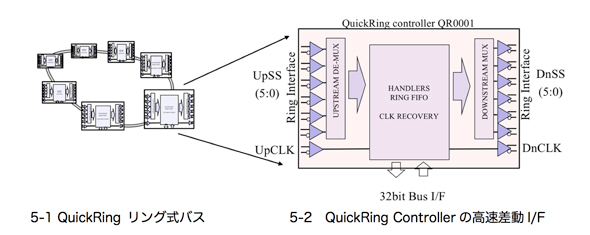

四半世紀前の1992年、Appleから高速伝送が可能なバスアーキテクチャー QuickRingが発表されました。QuickRingは図5-1のようにリング式のバス構成でLVDS物理層を採用し、基板間、筺体内、外部ケーブル使用で数メートルまでの筺体間で実効レート1.44Gビット/秒(以下、bps)の高速伝送が可能な仕様でした。

当時のPC標準バス ISAと比較するとスロット数、スピードは大幅に向上し、筺体間の接続までサポートしていました。

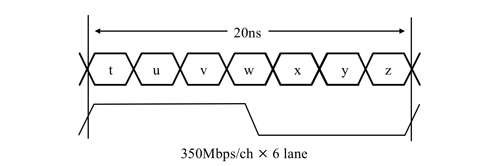

このコントローラーの物理層は図5-2のようにLVDSデータライン6本、LVDSクロック1本の構成です。またLVDSデータラインは、図6のように1クロックで7ビットを伝送しています。

このシリアル方式は現行のLVDS SerDesとほぼ同じで、四半世紀前にLVDS物理層を使用した高速バス伝送の方式は出来上がっていたといえるでしょう。このQuickRingのLVDSデータとLVDSクロックの構成、7倍のシリアルデータスピード、データスピードの1/7倍のLVDSクロックの仕様は、次に説明するLVDS SerDesに採用されています。

LVDS SerDesの登場

QuickRingコントローラーを開発したメーカーから1995年にLVDS SerDesが発表され、当時カラー化と高解像度が必要なラップトップPCのLCDパネルI/F採用されました。またオープンスタンダードであったため、多くの半導体メーカーから同機能のLVDS SerDes製品やIP内蔵LSIが発売され、相互接続が可能でした。筆者の勤めるザインエレクトロニクスも1997年に日本製として最初にLVDS SerDes THC63LVDシリーズを市場に投入し、その後、国内外のノートPCやPCモニター、薄型TVに標準的に使用されました。

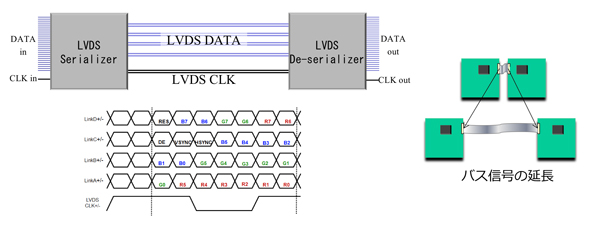

LVDS SerDesは図7のようにシリアライザに入力されるパラレルデータを、複数のLVDSレーンで1対あたり7倍のシリアル化を行い、データ同期のクロック信号も個別にLVDSで送る方式です。プロトコルやデータの種類、コーディングに一切制限がなく、バスデータから画像データまで、さまざまな多ビットパラレル信号を2点間の離れた場所に伝送する仮想ケーブルとして使用されています。

LVDS SerDesはLCD(Liquid Crystal Display)パネルの標準I/Fとしても知られています。LVDSは第3回目で紹介したように本来物理層の仕様を意味しますが、TVやPCなど標準的にLCDパネルを使用するアプリケーションではLVDS SerDesを略称LVDSと呼ぶほど、一般的なインターフェースとなっています。

LVDS SerDesのLVDSデータラインでは7倍速のシリアル化を行っていますが、パラレルバスと同様にクロックとデータラインが別送のため、ケーブルが長い場合やクロックスピードが高速になるとクロックラインとデータラインのスキュー(タイミングのずれ)が大きくなり、受信デバイスのACタイミング仕様を超えると正しくデータをサンプルすることができなくなります。

そのためLVDS SerDesのI/Fのままケーブルの延長やクロックスピードを速くすることは本来困難ですが、以下のような専用のリピーターデバイスを使用して対策することも可能です。

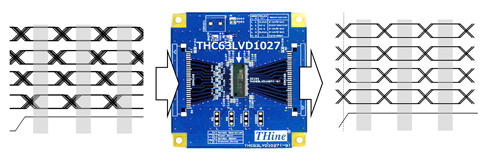

図8はLVDS SerDesの伝送路に追加して使用するLVDS SerDes専用のリピーター製品(THC63LVD1027)です。このリピーターは受信したLVDS SerDes信号のタイミングのずれを補正し再度送信を行うため、LVDS SerDesのケーブル延長やクロックスピードの高速化に対応するシステム構成が可能となります。また、1つのデシリアライザ入力から、タイミングを補正し2つのシリアライザ出力へ分配する機能も有しています。

Copyright © ITmedia, Inc. All Rights Reserved.

図5:QuickRing リング式バス(左)と、QuickRing Controllerの高速差動I/F(右)

図5:QuickRing リング式バス(左)と、QuickRing Controllerの高速差動I/F(右) 図6:QuickRing LVDSデータとLVDSクロックのタイミング

図6:QuickRing LVDSデータとLVDSクロックのタイミング 図7:LVDS SerDes

図7:LVDS SerDes 図8:LVDS SerDes専用 リピーター(

図8:LVDS SerDes専用 リピーター(