デジタル方式のイコライザー「FFE」「DFE」の概要:高速シリアル伝送技術講座(12)(2/3 ページ)

FFE(フィードフォアードイコライザー)

FFEはFIR(Finite Impulse Response:有限インパルス応答)フィルターを使用して伝送路のISIジッタを補償します。

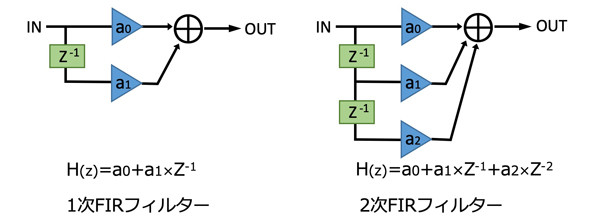

FIRフィルターはデジタルフィルターの一種で図3のようにZ-1部分でディレイし分岐した入力データをax部分でそれぞれ演算し最後に加算する構造になっています。このFIRフィルターは出力から入力に戻るフィードバックの経路がなく、信号は全て一方通行の構造になっています。

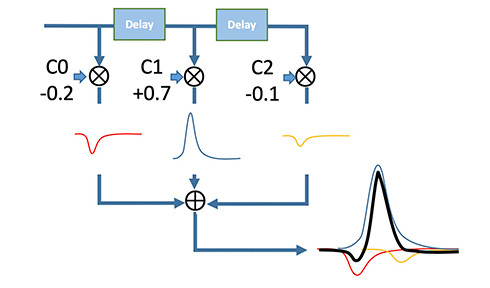

図4に3タップFFE回路のブロック図を示します。上記FIRフィルターと同じ構造で、入力信号に多段のディレイをかけ、それぞれの分離パス(タップ)の⊗部で減衰、増幅、反転の処理を行い、最後に⊕部ですべて加算してアナログ的な信号波形を作り出力します。

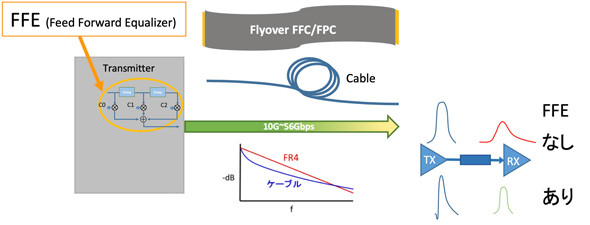

FFEは送信側、受信側ともに実装可能ですが、ここでは送信側への実装として説明していきます。

図4の3タップFFEの動作ではディレイした入力信号を⊗部C0、C1、C2で各係数をかけて、増幅、減衰、反転を行います。1タップ目は赤の波形、2タップ目は青の波形、3タップ目は黄の波形を作ります。この3つの信号を⊕部で加算すると黒の出力波形になります。この出力波形の例では1タップ目のC0を反転の-0.2とし、プリシュートを作り、また3タップ目C2を-0.1とし2タップ目の立下り信号のエッジレートを上げるように調整しています。

図5左はFFEのトランスミッタへの実装、図5右は高速の信号がインサーションロスのある伝送路を通過した際の受信波形(上)と送信端FFEでISIジッタを補償した波形(下)を示しています。

入力信号を順次ディレイし、⊕部で加算する本数(タップ数)が多くなると時間軸は延びますが波形の多様な調整が可能となります。ただしタップ数が増えるとともに消費電力も大きくなるため、実際の設計では2タップや3タップが多いようです。2タップの場合は、以前に説明したプリ(デ)エンファシスドライバの波形と同じ機能になります。

3タップ構成では図4のように最初のタップで中央の2タップ目波形の前の部分に高周波を強調するプリシュート波形の追加が可能になります。また、最後の3タップ目で中央の2タップ目からの振幅を自由に変化させるより、細かなディエンファシスの波形もディレイ時間単位で調整できるようになります。

2タップ構成でも、出力ドライバが矩形波の高速なエッジレートを持ち、最大周波数で振幅が十分に大きく、また伝送路の逆特性になるような大きな減衰に対応した係数のフィルターを使用し、ハイパスフィルターを通したようなアナログ的な出力波形を作ることができれば、受信端の振幅はとても小さくなるものの、送信側のFFEだけでも−20dB程度のインサーションロスのISIジッタにも対応できます。

Copyright © ITmedia, Inc. All Rights Reserved.

図3:FIRフィルター

図3:FIRフィルター 図4:3タップFFEとその動作

図4:3タップFFEとその動作 図5:送信端FFEと受信波形

図5:送信端FFEと受信波形